Understanding NI CompactRIO Scan Mode

Overview

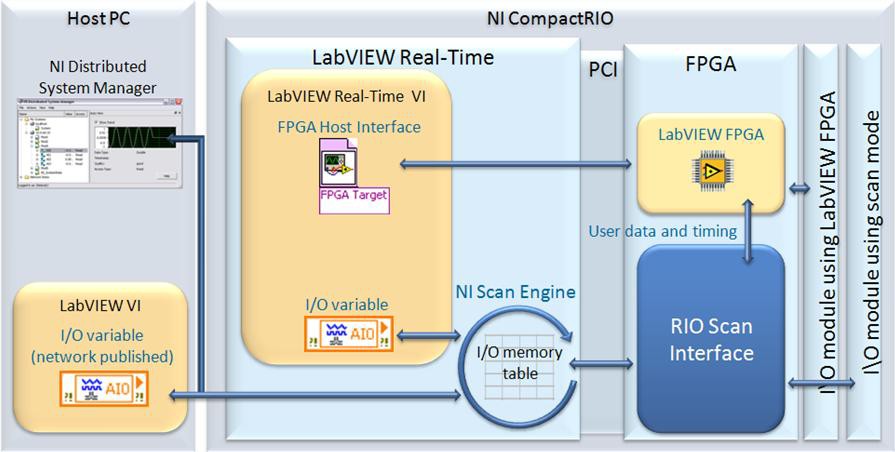

The LabVIEW Real-Time Module 8.6 introduced powerful new features for programming CompactRIO hardware that reduce development time and complexity as well as provide tools for monitoring and maintaining CompactRIO applications. This functionality is powered by two technologies in LabVIEW, the NI Scan Engine and the RIO Scan Interface. The NI Scan Engine is a new component of LabVIEW Real-Time that scans I/O values into memory at a rate you specify. The RIO Scan Interface is a set of FPGA intellectual property (IP) developed by NI that is downloaded to the CompactRIO FPGA and is responsible for I/O module detection, timing, synchronization, and communication.

Using CompactRIO Scan Mode, you can choose between accessing each I/O module directly in LabVIEW Real-Time and host applications with no FPGA programming or in LabVIEW FPGA for maximum flexibility and performance. You can also use new test panels and I/O forcing functionality to get up and running quickly, perform advanced debugging, and monitor system performance.

This paper discusses the use cases, operation, and architecture of the NI Scan Engine and RIO Scan Interface.

Contents

- When Should I Use CompactRIO Scan Mode?

- CompactRIO Scan Mode Features

- Debug and Monitor I/O with the NI Distributed System Manager

- Using Hybrid Mode to Access Modules With Scan Mode and LabVIEW FPGA

- CompactRIO Scan Mode Architecture

- Footnotes and Related Resources

When Should I Use CompactRIO Scan Mode?

There are three ways to access module I/O on a CompactRIO device, listed below. All CompactRIO devices can access the CompactRIO Scan Engine and LabVIEW FPGA. The CompactRIO 904x line was the first to introduce DAQmx functionality.

- Scan Engine (IO Variable) – Designed primarily for migration and initial development. Control loops up to 1 kHz1, higher on performance controllers.

- Real-Time (NI-DAQmx) – Designed for waveform acquisition and access to hardware timing. Control loops up to 5kHz.

- LabVIEW FPGA Module – Designed for custom protocols, co-processing, and reliability. Control loops in the MHz range.

CompactRIO Scan Mode is designed for applications requiring synchronous I/O updates at rates of up to 1 kHz1. The primary benefit to using the Scan Mode is ease of development, since it does not require FPGA programming. With the I/O forcing and test panel functionality of the system manager, you can also use scan mode for initial setup, system performance monitoring, and advanced troubleshooting.

If your CompactRIO controller supports NI-DAQmx, you can create hardware-timed control loops with faster rates (up to 5KHz). The NI-DAQmx API also allows for easy development which does not require FPGA programming. NI-DAQmx is a great fit for data acquisition and control loops with moderate rates, on I/O modules where FPGA control is not required. Click here to learn more about using NI-DAQmx with CompactRIO.

For applications with higher-performance requirements, such as analog streaming at nearly 1 MHz, high-speed PID control loops more than 1 kHz, custom hardware analysis and signal processing, or I/O modules not supported by scan mode, use the LabVIEW FPGA Module with scan mode. You can also offload processing from the real-time controller with the LabVIEW FPGA Module. Click here to watch a video series on getting started with LabVIEW FPGA.

CompactRIO Scan Mode Features

Prior to LabVIEW 8.6, CompactRIO I/O could only be accessed by programming the FPGA, then using the LabVIEW FPGA Interface VIs in LabVIEW Real-Time. CompactRIO Scan Mode was introduced in LabVIEW 8.6 to allow users to read/write data without needing to program their FPGA. This reduces development time and complexity for applications that do not require the power and loop rates of the on-board FPGA.

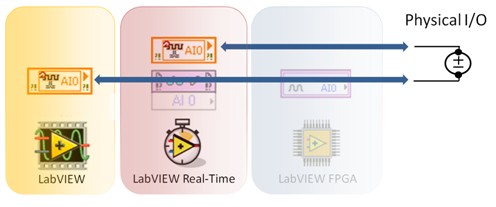

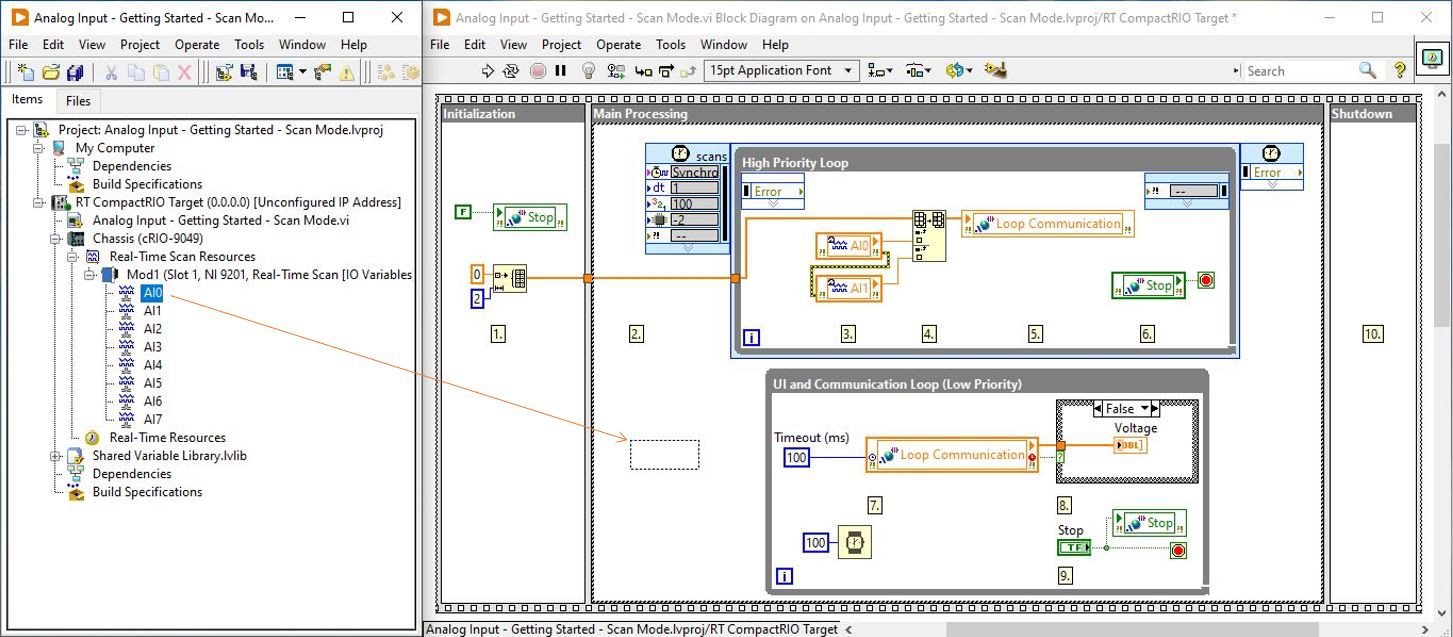

Figure 1. CompactRIO Scan Mode provides access to I/O directly from LabVIEW host VIs and LabVIEW Real-Time VIs without needing to program or compile FPGA code.

CompactRIO Scan Mode automatically detects the I/O modules in your CompactRIO chassis and adds them to the LabVIEW Project. You can then drag and drop the I/O variables onto your LabVIEW Real-Time and host VI block diagrams. These I/O variables allow you to instantly read and write scaled, calibrated I/O data without any FPGA programming or compiling. You can create aliases of I/O variables to provide an additional layer of abstraction from the physical I/O channel. Linear and square root scaling are available on I/O variables and aliases.

Figure 2. Access I/O directly in LabVIEW Real-Time by dragging and dropping I/O variables to your block diagram.

The NI Scan Engine, a component of LabVIEW Real-Time, updates the I/O variable values at a rate you specify (up to 1 kHz1). All channel scans are hardware-timed with module-to-module synchronization. You can configure the scan engine from the LabVIEW Project or programmatically. The scan engine also provides a timed-loop timing source, so you can synchronize code with I/O updates for low-jitter control applications.

CompactRIO Scan Mode can also add counter, quadrature encoder, and pulse-width modulation (PWM) functionality to any existing eight-channel digital NI C Series Module without requiring any FPGA programming. You configure these specialty digital functions from the LabVIEW Project, but they run on the FPGA for accuracy and speed. Now, without compiling, you can perform up to 1 MHz edge counting, pulse-width and frequency measurements, quadrature decoding, and PWM control.

Counter functionality includes:

- 1 MHz counting on eight channels

- 32-bit register, with programmable terminal count

- Configurable terminal count and terminal count behavior

- Configurable count edge (rising, falling, or both), source, and gate

- Period, PWM, and frequency measurements with configurable timebase

Quadrature encoder functionality includes:

- 1 MHz max quad count rate

- 32-bit count register

- 32-bit velocity measurement register

- Configurable velocity measurement timebase (256 µs, 512 µs, ... 16384 µs, or 32768 µs)

- X4 encoding

- Two quad channels with A+B+Index inputs per module

- Selectable encoder polarity

PWM-specific features

- Eight output channels

- Per-channel duty-cycle and period configuration

- Configurable frequency period (1 Hz, 50 Hz, 250 Hz, 500 Hz, 1 kHz, 5 kHz, 10 kHz, or 20 kHz)

There are some performance trade-offs when using CompactRIO Scan Mode. For example, the specialty digital functionality supports up to 1 MHz counters versus the 20 MHz counters achievable with LabVIEW FPGA. The scan engine uses system resources, which include FPGA space, two DMA channels, memory, and an amount of CPU time that scales with the scan rate. The space consumed by the RSI, on the FPGA, scales with the number of modules using scan mode.

Debug and Monitor I/O with the NI Distributed System Manager

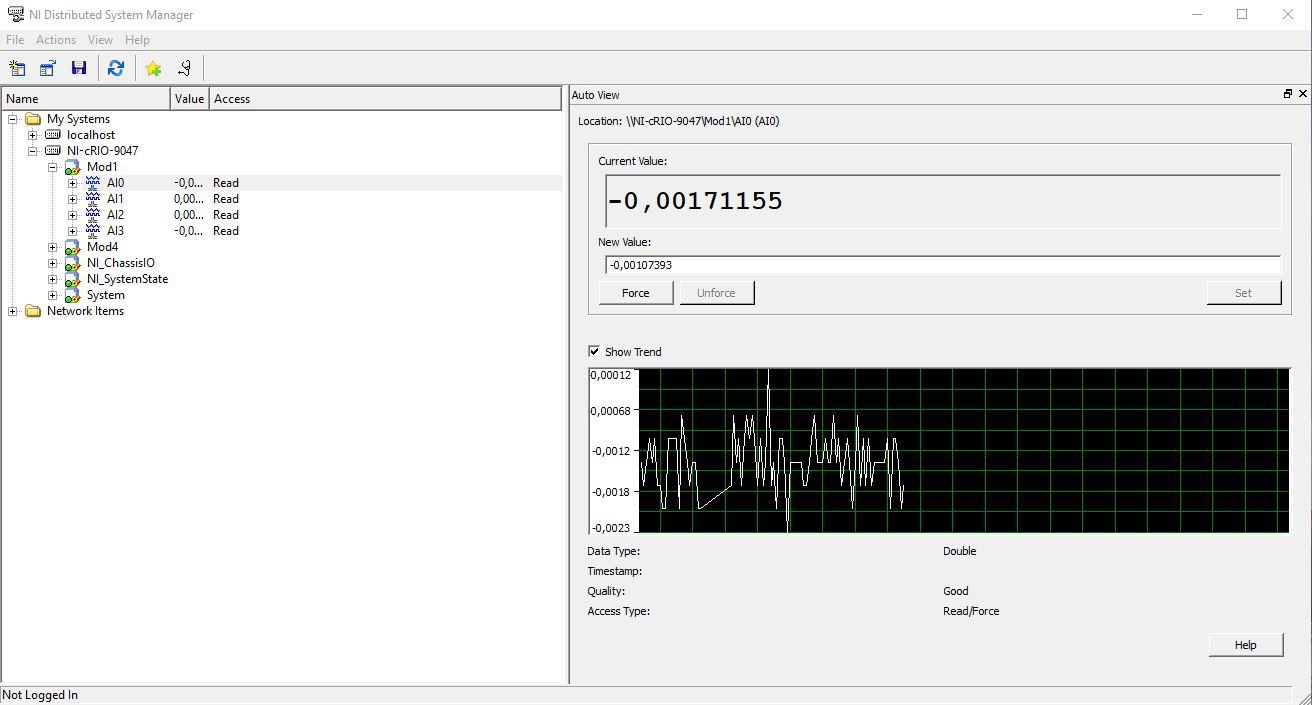

The NI Distributed System Manager provides a central location for monitoring systems on the network and managing published data. The Distributed System Manager offers test panels for C Series Modules using CompactRIO Scan Mode. As soon as your system is available on the network, you have access to real-time and historical-trend I/O values, so you can quickly verify your connections and signal integrity. In addition to test panels, the system manager also gives visibility into memory usage and processor load for CompactRIO controllers.

Figure 3. The new NI Distributed System Manager helps you get up and running quickly by adding test panels to CompactRIO.

Using the NI Distributed System Manager with CompactRIO Scan Mode provides I/O forcing, which is a debugging tool you can use to override the value of an I/O variable without stopping or changing your real-time application. You can force inputs to test the response of your application without a physical stimulus, as well as force outputs to override program output values. You can force channel values using the system manager or with new I/O forcing VIs.

Using Hybrid Mode to Access Modules With Scan Mode and LabVIEW FPGA

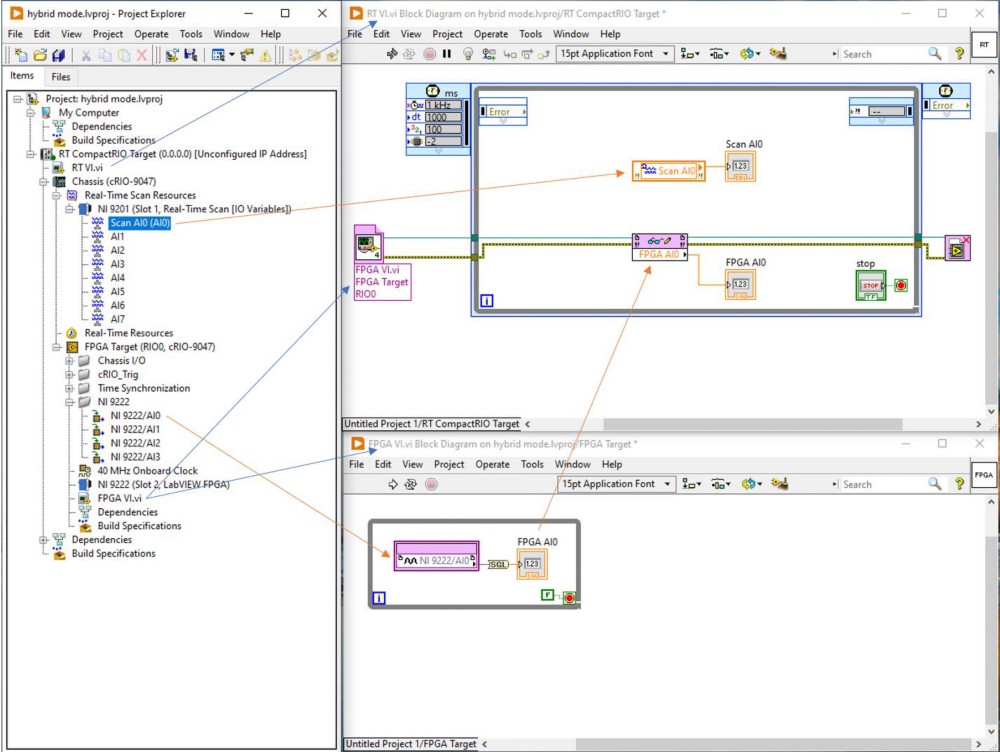

Some applications benefit from having some I/O modules accessed with CompactRIO Scan Mode, while other modules are accessed using LabVIEW FPGA. This is known as "Hybrid Mode," and is helpful when some modules require LabVIEW FPGA's custom triggering, hardware-based analysis or high-speed analog streaming.

To use I/O modules in LabVIEW FPGA Mode, simply drag the module to the FPGA target in the LabVIEW Project, removing it from scan mode. Then use LabVIEW FPGA to program the modules and use I/O variables to read and write I/O on the remaining modules.

Figure 4. This VI accesses I/O with CompactRIO Scan Mode while computing the fast Fourier transform of an acceleration input with LabVIEW FPGA.

When using LabVIEW FPGA Mode on one or more modules, the CompactRIO Scan Mode logic on the FPGA, known as the RIO Scan Interface, is compiled with the LabVIEW FPGA VI into a single FPGA application. This combination of logic has an impact on compilation time and the DMA FIFOs available for data transfer. If no modules are configured to use scan mode, the RIO Scan Interface is not included in the compile.

You can create user-defined I/O variables to provide communication between your real-time and FPGA VIs. This provides a way for data from the FPGA VI to be inserted into the scan engine and read out in LabVIEW Real-Time, using the same I/O variable API used for scan mode I/O. These I/O variables can also pass data from a real-time VI to the FPGA; however, each I/O variable is unidirectional. Methods are also provided to synchronize your LabVIEW FPGA code to the RIO Scan Interface I/O updates.

For example, suppose a CompactRIO system is using LabVIEW FPGA to monitor an accelerometer at 50kHz and calculate the RMS on the fly, The RMS calculation on the FPGA can be synchronized to the FPGA scan mode logic and written to a user-defined I/O variable, which is then accessed in a LabVIEW Real-Time VI.

CompactRIO Scan Mode Architecture

RIO Scan Interface

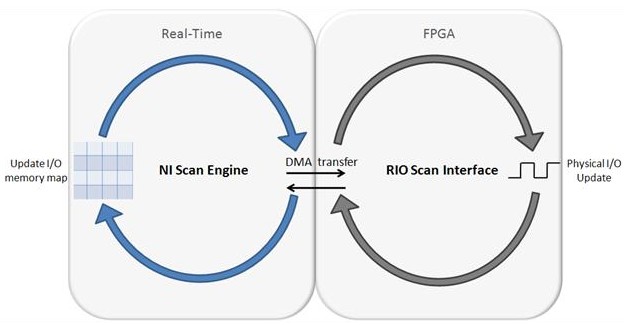

CompactRIO Scan Mode is powered by two technologies, the RIO Scan Interface and the NI Scan Engine, which work together to provide access to physical I/O on CompactRIO. The RIO Scan Interface is a set of FPGA intellectual property (IP) developed by NI that is downloaded to the CompactRIO FPGA and is responsible for I/O module detection, timing, synchronization, and communication. The RIO Scan Interface runs a hardware-timed scan loop, which updates the physical I/O values. Two DMA channels are used to transport I/O data between the FPGA and real-time operating system (RTOS). This implementation provides hardware-timed I/O updates at the pin with less that 500ns of jitter.

Figure 5. Synchronization of the NI Scan Engine and RIO Scan Interface maintains less than 500ns of jitter at the pin.

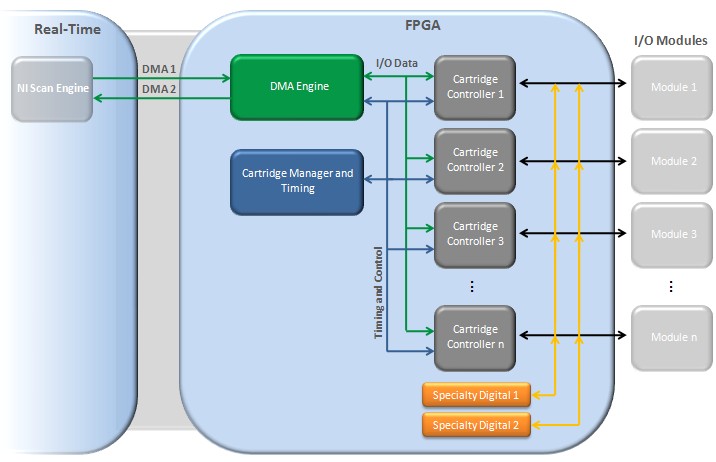

The RIO Scan Interface contains several components that enable the flexibility and performance it provides. Each I/O module communicates directly with a cartridge controller responsible for detecting the module type and communicating I/O data to and from the module. The cartridge controller is a “soft-core” eight-bit microcontroller, which is instantiated in the FPGA, allowing you to use any supported I/O module without compiling. There are also two prebuilt specialty digital blocks in the RIO Scan Interface, which provide high-speed counter, pulse width modulation (PWM), and quadrature encoder input functionality to any eight channel (or less) digital C Series Module. The specialty digital blocks can be routed to any two slots in the CompactRIO chassis. Additional specialty digital blocks can be added using the LabVIEW FPGA Module. Each cartridge controller communicates with a single cartridge manager, which controls the hardware scan timing, synchronization of I/O modules, and synchronization with the NI Scan Engine. A DMA engine also communicates with the cartridge controllers and cartridge manager to transfer data to and from the real-time controller.

Figure 6. The RIO Scan Interface contains several components, all of which are instantiated in the FPGA.

NI Scan Engine

The NI Scan Engine is a component of LabVIEW Real-Time that runs at a priority above time critical or between time critical and timed structures, which you can configure. Each time the RIO Scan Interface has finished the latest I/O scan, LabVIEW adds the I/O variables to a global scan engine memory map and updates the values of all I/O variables concurrently. However, you can configure each I/O variable node to use either scanned access or direct access. By default, LabVIEW configures I/O variable nodes to use scanned I/O, which uses the scan engine memory map to perform non-blocking I/O reads and writes (see Figure 5). Direct I/O access bypasses the scan engine memory map and communicates directly with the I/O device driver to perform blocking I/O reads and writes (see Figure 5). The NI Scan Engine also publishes the I/O variables to the network, making them available for reading and writing in host applications, test panels, and I/O forcing. The scan engine, not the LabVIEW shared variable engine, handles the network publishing of the I/O variables, which you can disable from the I/O variable properties page.

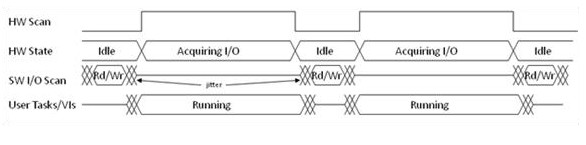

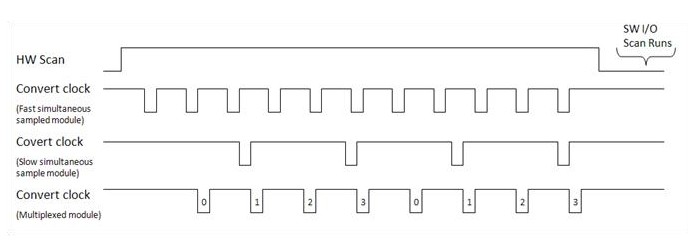

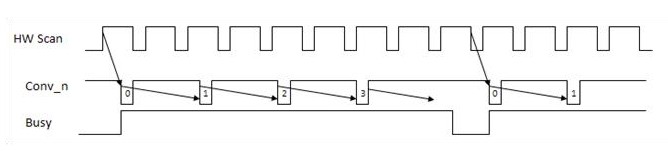

A timing signal within the FPGA is asserted when the hardware is busy acquiring data from the I/O modules. The period of this hardware scan is determined by the scan rate you specify in the scan engine properties. At the end of each hardware scan the scan engine transfers I/O data between the controller and the FPGA.

Figure 7. A timing signal within the FPGA determines when I/O data is transferred from the FPGA to the real-time controller.

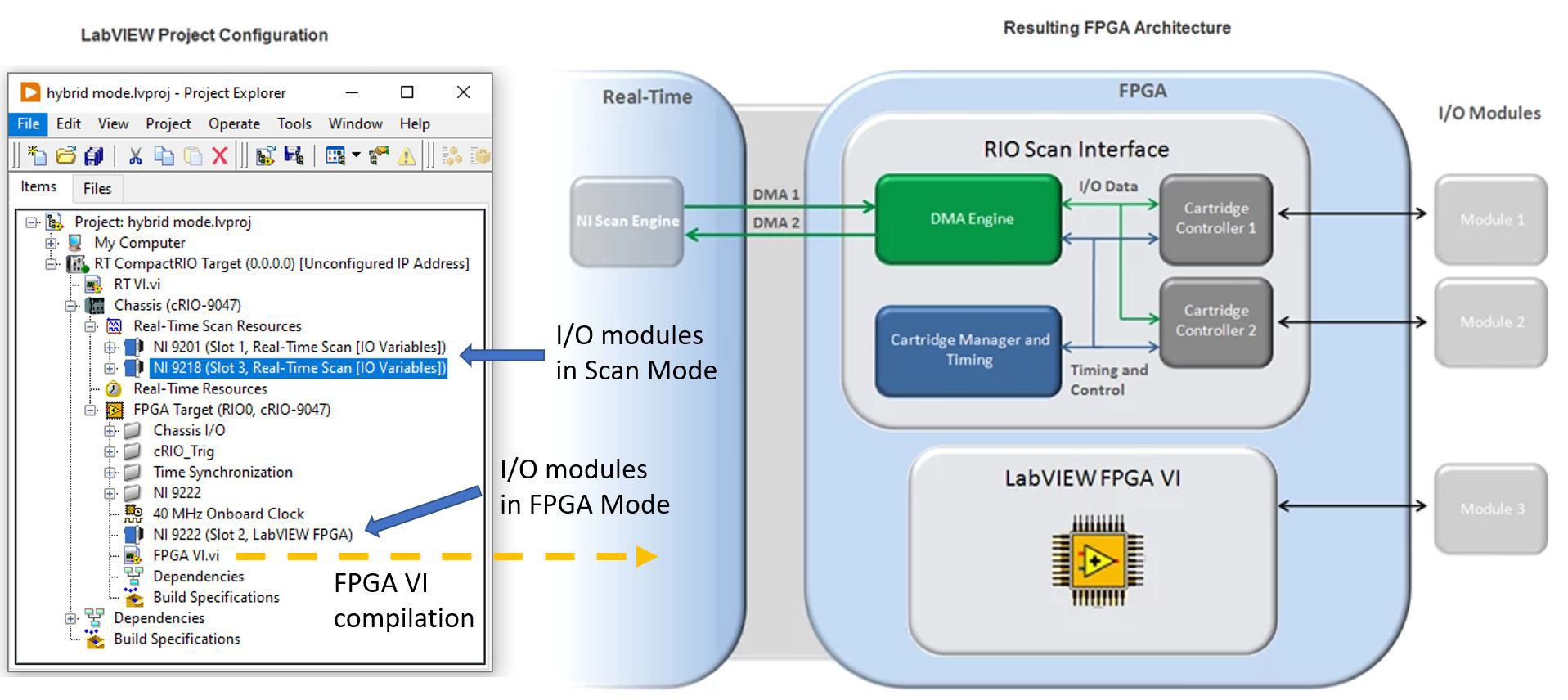

Hybrid Mode (Scan Mode with LabVIEW FPGA)

One of the most powerful features of CompactRIO Scan Mode is the ability to choose individual modules to program directly with the LabVIEW FPGA Module. Using this approach, the modules you select to program directly with LabVIEW FPGA are removed from the I/O scan and the remaining modules communicate with the RIO Scan Interface.

Figure 8. CompactRIO Hybrid Mode under the Hood.

When you compile your LabVIEW FPGA VI, if any I/O modules are configured to use scan mode, then the necessary components of the RIO Scan Interface will be included in the compile. The result is a single bit file that supports the scan mode features for modules configured to use scan mode, as well as your custom FPGA logic that communicates directly with the remaining I/O modules. LabVIEW is intelligent about the compile and only includes the required components of the RIO Scan Interface for a given configuration. For example, if you compile an FPGA VI that only uses one module in scan mode, then only one cartridge controller will be included in the RIO Scan Interface. Specialty digital blocks are also removed if not configured. Therefore, the amount of FPGA space consumed by the RIO Scan Interface, when compiling an FPGA VI, scales with number of modules using scan mode.

Figure 9. When accessing I/O modules in both Scan Mode and LabVIEW FPGA, only required RIO Scan Interface components are compiled.

I/O Timing

The convert clocks on all I/O modules are free running when the hardware scan signal is asserted. Each I/O module type has individual conversion timing, and modules of the same type have synchronized conversions. When the hardware timing signal on the FPGA is unasserted the latest I/O conversion value is transferred to the NI Scan Engine. Each module performs as many conversions as possible to provide the most recent I/O values to I/O variables configured for direct I/O access, which bypasses the scan and reads directly from hardware.

Figure 10. Input module timing.

A slow input module may take several hardware scan periods to convert a single channel. In this case the hardware scan triggers a sequence of converts on all channels. No channel values are copied to the scan engine until all channels have finished being converted, then all channel values are transferred together.

Figure 11. Input timing for a slow module.

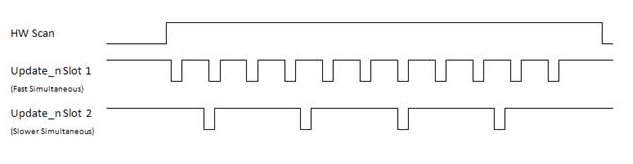

Output module timing is like input module timing, but the conversions are left justified so that output values are written immediately at the beginning of a scan. Each module performs as many updates as possible during the hardware scan, so that values written to I/O variables configured for direct I/O access will update as quickly as possible.

Figure 12. Output module timing.

Footnotes and Related Resources

1 1 kHz rates are a soft upper limit. In legacy versions of LabVIEW, this was an enforced limit. With the release of cRIO-908x, cRIO-903x, and cRIO-904x controller lines, loops over 1 kHz are achievable. The maximum rate the Scan Engine (and subsequent plugins, for instance the RIO Scan Interface) can reliably reach are dependent on many factors. These include overall application, use of other Scan Engine plugins, number and type of channels, processor model, processor core assignments, use of timestamps on I/O Variables, and network publishing of the I/O data. Please see NI Scan Engine Performance, linked below.