Explicación del serial de alta velocidad

Información general

El serial de alta velocidad es una tecnología cada vez más popular que reduce el tamaño del dispositivo y aumenta las velocidades de comunicación de datos. Este documento explora los conceptos fundamentales de los enlaces de comunicación serial de alta velocidad.

Contenido

- La necesidad del serial de alta velocidad

- Capas de enlaces seriales de alta velocidad

- Conclusiones

- Contenido relacionado

La necesidad del serial de alta velocidad

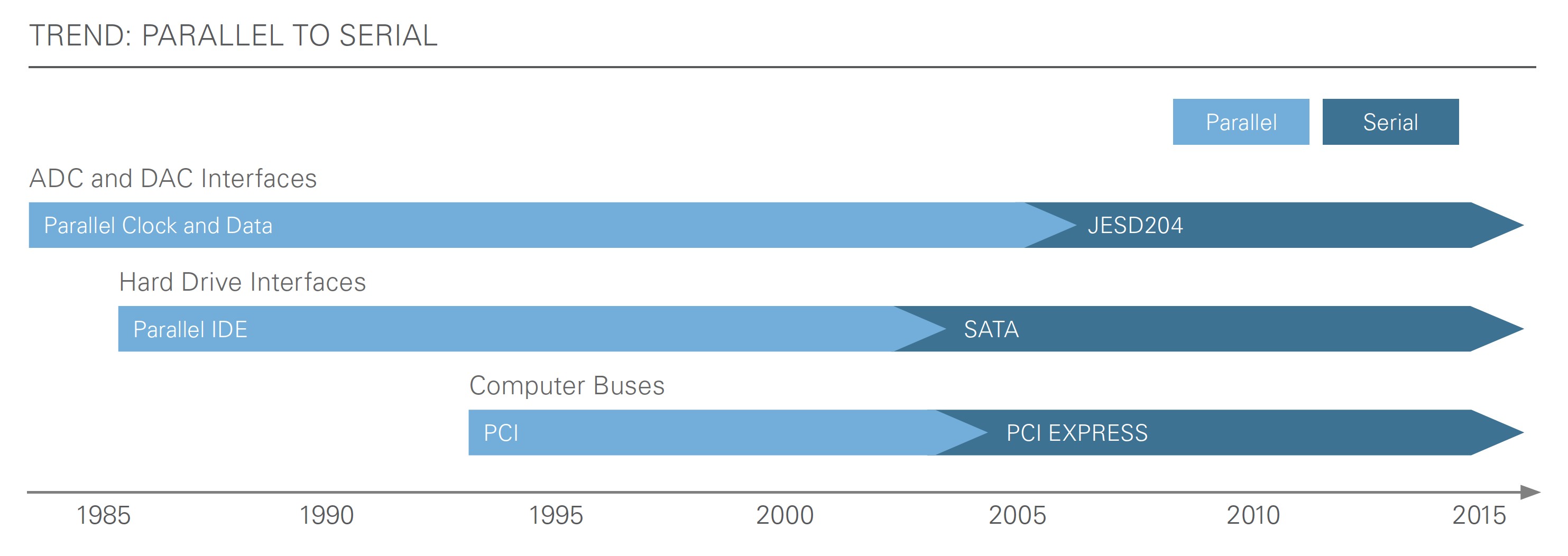

Los consumidores exigen continuamente un mejor rendimiento en un tamaño más pequeño con requisitos de energía reducidos. A principios del año 2000, estas demandas en un mundo de big data provocaron un cambio drástico de los buses de comunicación digital serial en paralelo a los de alta velocidad. Esto, a su vez, ha llevado a dispositivos con tamaños mucho más pequeños, un rendimiento de datos mucho mayor y menores requisitos de energía. Estas características hacen posible muchas de las tecnologías que los consumidores aprovechan hoy en día, como SATA, USB y PCI Express.

Figura 1: A principios del año 2000, el mercado comenzó a hacer la transición de los estándares comunes de comunicación en paralelo a los estándares seriales.

Ventajas

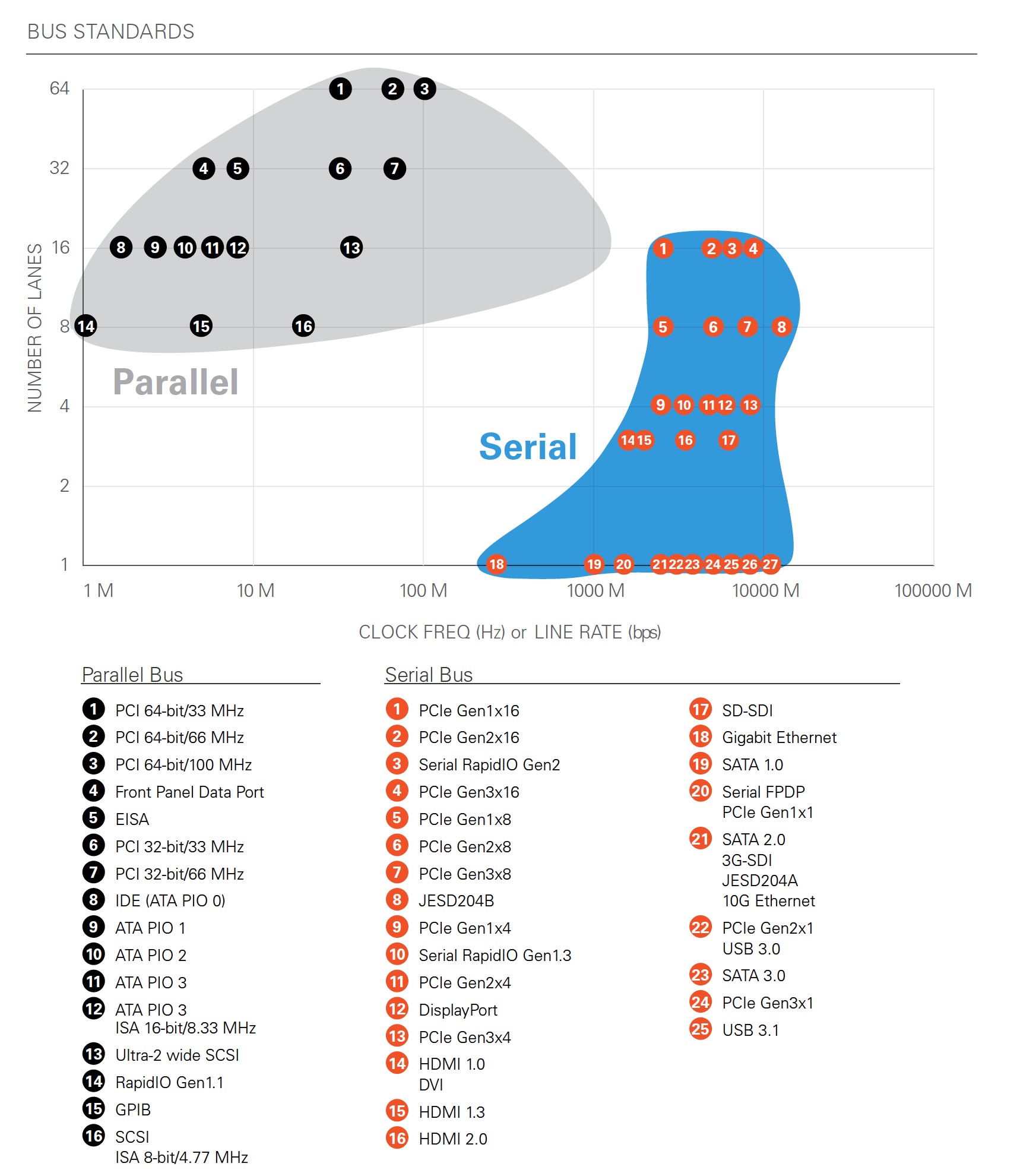

La limitación física en las velocidades de reloj de los buses paralelos es de alrededor de 1 GHz a 2 GHz debido al desfase introducido por el reloj individual y las líneas de datos que causa errores de bits a velocidades más rápidas. Los buses seriales de alta velocidad envían datos codificados que contienen datos e información de reloj en una sola señal diferencial, por lo que los ingenieros pueden evitar las limitaciones de velocidad en los buses paralelos. Hoy en día, son comunes los enlaces seriales de alta velocidad con líneas de datos que se ejecutan a 10 Gbps. Además, múltiples líneas de enlaces seriales pueden unirse para formar enlaces de comunicación con transferencias de datos más altas.

Al serializar los datos y enviarlos a velocidades más rápidas, se puede reducir la cantidad de pines en los circuitos integrados (IC), lo que ayuda a reducir el tamaño del dispositivo. Es más, ya que las líneas seriales pueden operar a una velocidad de reloj mucho más alta, usted también puede alcanzar un mejor rendimiento de datos de lo que era posible con buses paralelos.

Figura 2: Esta tabla muestra estándares de buses conocidos y sus respectivos números de líneas en comparación con velocidades de línea. Los estándares seriales pueden transmitir a velocidades de línea mucho más altas que los paralelos, dando como resultado un rendimiento más alto.

Desventajas

Aunque la cantidad reducida de pines puede reducir las complejidades del diseño, las velocidades más rápidas requeridas representan desafíos de diseño adicionales. Con diseños que alcanzan frecuencias de RF, usted debe tener consideraciones analógicas similares a las que tendría para las aplicaciones de RF para garantizar una integridad de la señal adecuada. Para disminuir estos problemas de integridad de la señal, los enlaces seriales de alta velocidad implementan técnicas como codificación, pre-análisis y ecualización.

Capas de enlaces seriales de alta velocidad

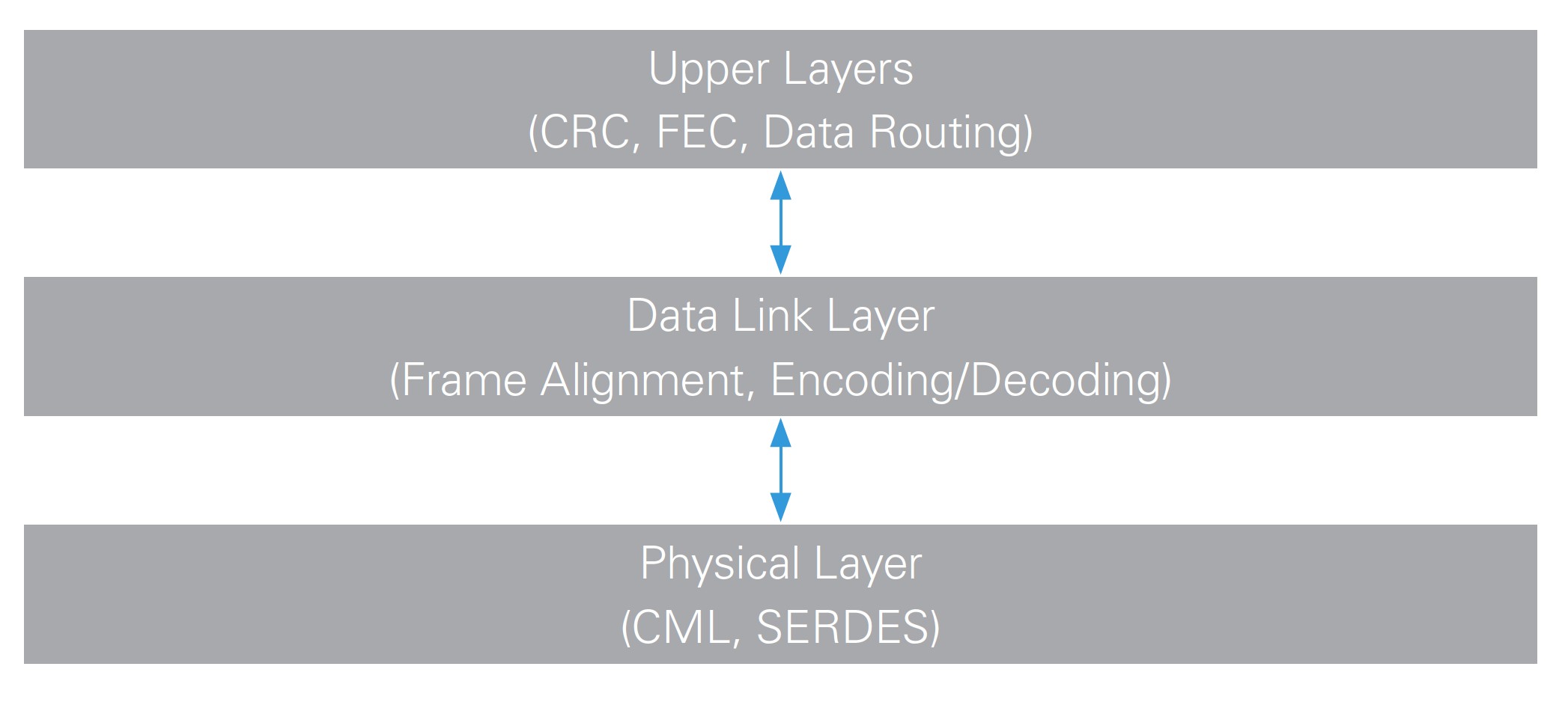

Para que una conexión serial funcione, cada terminal debe estar de acuerdo para operar dentro de parámetros específicos. Usted puede abstraer estos parámetros a múltiples capas funcionales.

Figura 3: Puede agregar capas por encima de la capa física y de la capa de enlace de datos. Estas capas varían por protocolo y aplicación y suelen ser personalizadas más comúnmente.

Capa física

La capa física garantiza la compatibilidad eléctrica entre dispositivos y presenta bits sincronizados a la capa de enlace de datos.

Interfaz eléctrica

Los diferentes protocolos seriales de alta velocidad definen los diferentes requisitos para la interfaz eléctrica del transmisor y del receptor. Esto garantiza la compatibilidad eléctrica al conectar el dispositivo transmisor al receptor. La señal eléctrica para enlaces seriales de alta velocidad tiene dificultad para alcanzar tiempos de incremento y reducción extremadamente rápidos que son necesarios para comunicar a velocidades arriba de 1 Gbps, disminuir emisiones electromagnéticas y mejorar inmunidad de ruido al rechazar el ruido de modo común. Además, los voltajes pico-a-pico rara vez llegan arriba de 1V a estas velocidades y los estándares eléctricos generalmente son señalamiento diferencial de bajo voltaje (LVDS), lógica de emisores acoplados (ECL) o lógica de modo de corriente (CML).

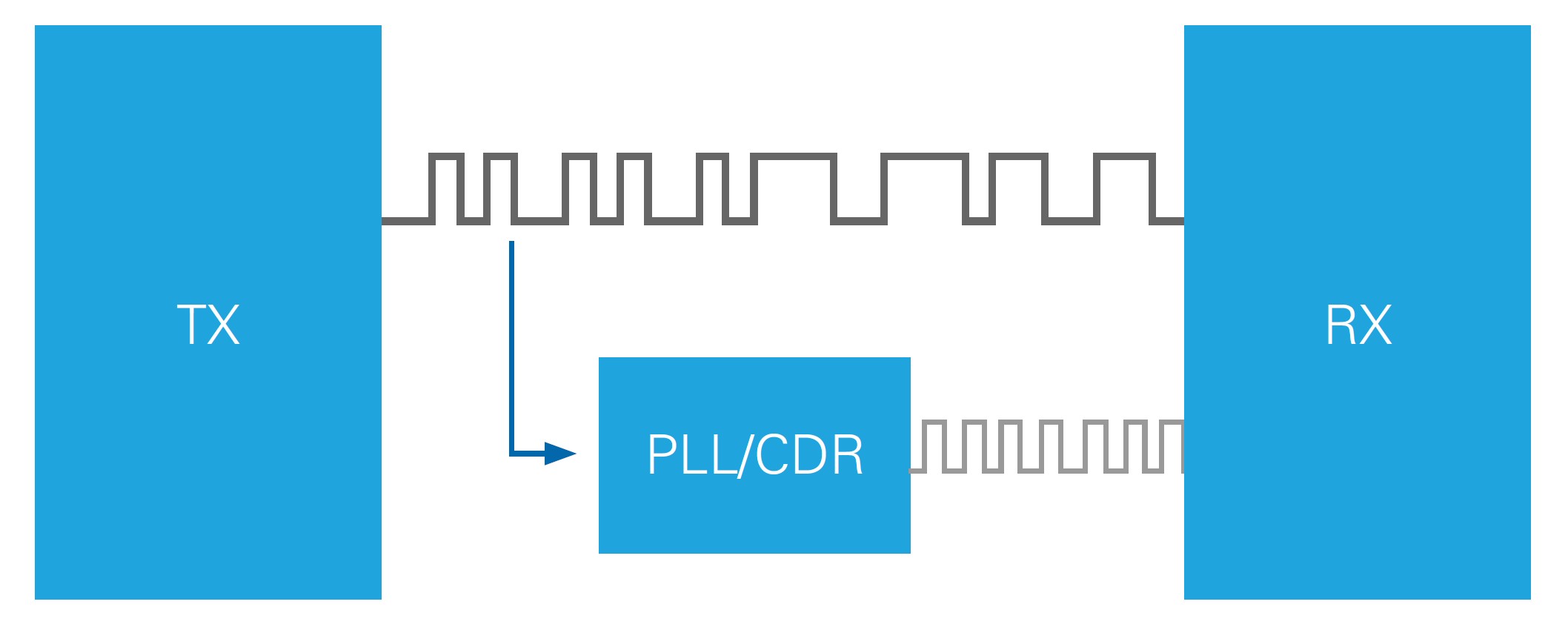

Recuperación de datos y reloj

Otra característica importante de la capa física para enlaces seriales de alta velocidad es la recuperación de datos y reloj (CDR). CDR es la habilidad del dispositivo de recepción de cronometrar la transferencia de datos entrantes sin la necesidad de una señal actual de reloj. La capa de enlace de datos ayuda a lograr esto al garantizar transiciones frecuentes de bits a través de codificación. Esto permite que los circuitos de ciclo enlazado a fase (PLL) y de interpolador de fase (PI) vuelvan a crear el reloj de transmisión y lo utilicen para capturar el flujo de datos entrante con un error de temporización mínimo.

Figura 4: Ya que la codificación en la capa de enlace de datos garantiza transiciones frecuentes entre 0 y 1, los circuitos CDR pueden realizar PLL al flujo de bits entrantes y muestrear de forma síncrona los bits de datos codificados.

Consideraciones para la integridad de la señal

Transmitir datos con bits en transición a velocidades de 5 GHz o más crea desafíos en el diseño analógico. Debido a que las velocidades de transmisión ahora están en rangos de frecuencia típicos de los diseños de RF, surgen problemas de integridad de la señal. Debe utilizar PCBs, conectores y cables de alta calidad para comunicarse con éxito a estas altas velocidades de datos. Además, los diseñadores de PCB deben comprender la teoría de la línea de transmisión al diseñar para enlaces seriales de alta velocidad. Deben poder evitar stubs, desajustes de impedancia y desajustes de longitud de traza y utilizar las técnicas adecuadas para minimizar las distorsiones de la señal.

Ecualización

La ecualización es el proceso de contrarrestar el comportamiento eléctrico de un canal para incrementar su respuesta de frecuencia. Esto puede ocurrir ya sea del lado del transmisor o del receptor del enlace de comunicación para mejorar el margen del enlace, pero el término ecualización generalmente se usa al hacer referencia al receptor. Cuando la señal serial de alta velocidad viaja por las trazas de la PCB, a través de conectores y cables y hacia el receptor, la atenuación no afecta todos los componentes de frecuencia de la señal por igual y causa distorsión de la señal. La configuración de la ecualización en los transceptores multi-gigabit (MGTs) puede agregar ganancia o atenuación a diferentes frecuencias de la señal antes de ser muestreada para mejorar el margen del enlace y la señal. Muchos MGTs tienen auto-ecualización que puede detectar automáticamente y actualizar continuamente los ecualizadores a su configuración ideal.

Pre-énfasis

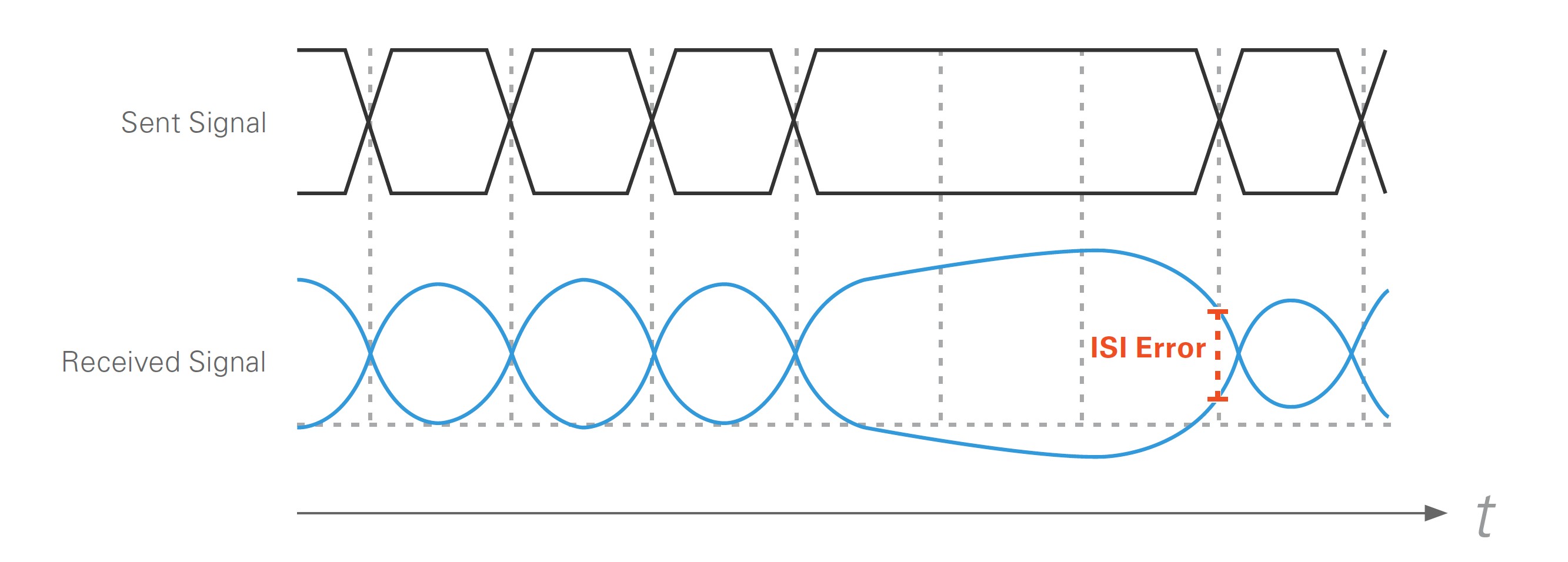

El pre-énfasis generalmente se refiere a la ecualización en el lado del transmisor de un enlace serial de alta velocidad. Se utiliza principalmente para superar los desafíos analógicos similares a los que presenta la interferencia entre símbolos (ISI). A rápidas velocidades de línea, los bits de datos comienzan a afectarse uno a otro al transmitirse. Por ejemplo, si existen tres 1 transmitidos sucesivamente, seguidos por un solo 0, es difícil para el 0 ser impulsado rápidamente porque la línea ha creado una polarización positiva.

Figura 5: La degradación de la señal debida a ISI se produce cuando la falta de transiciones de bits hace que la línea genere una polarización, lo que dificulta que la primera transición al bit opuesto se produzca rápidamente.

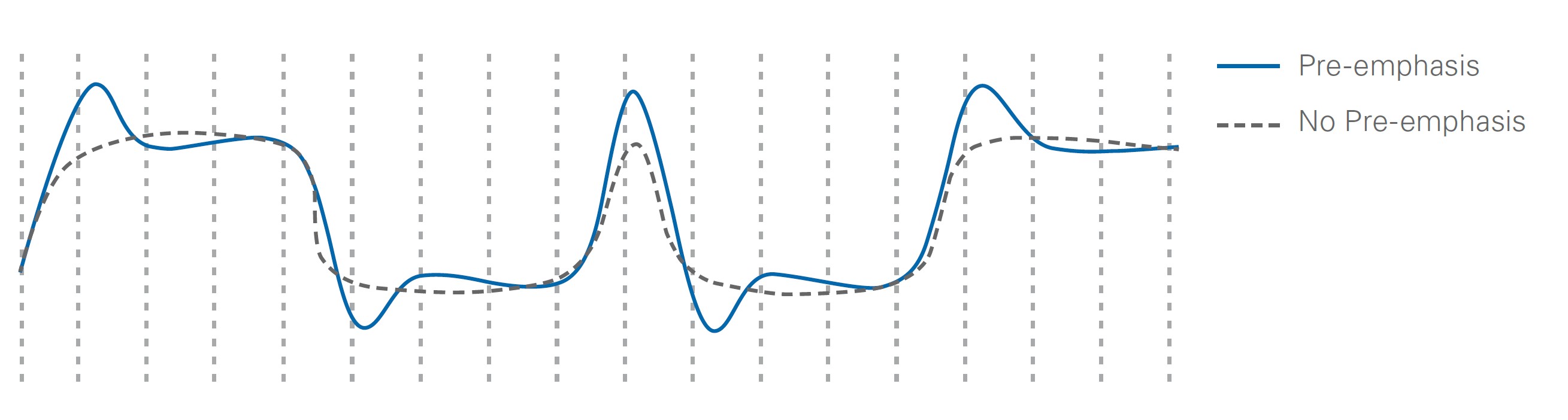

Usted tiene dos formas de superar el ISI. Conociendo que solamente el primer bit tiene problemas después de una transición de bajo a alto o alto a bajo, usted puede amplificar solamente el primer bit después de una transición. Esto da como resultado la señal que se muestra en la Figura 6.

Figura 6: El pre-énfasis está diseñado para exagerar el primer bit después de una transición de una señal. Esto ayuda a disminuir problemas como el ISI.

Un enfoque más común para lograr una forma de onda similar es atenuar los bits después de la primera transición en lugar de amplificar el primer bit. Los filtros de paso alto logran esto, ya que los bits en transición (frecuencia más alta) son menos atenuados que los bits que no están en transición.

Capa de enlace de datos

La capa de enlace de datos manipula los datos para mejorar la integridad de la señal, garantizar una comunicación exitosa y asignar bits físicos a los datos. Las funciones para habilitar esto son los esquemas de codificación y control de caracteres para alineamiento, corrección de reloj y unión de canales.

Esquemas de codificación

El objetivo de codificar es garantizar transiciones frecuentes de bits para lograr una CDR exitosa, así como garantizar un equilibrio de DC para los datos. Para garantizar una CDR exitosa, el esquema de codificación necesita garantizar que la señal de datos tendrá suficientes transiciones para que el circuito CDR permanezca enlazado en fase con el flujo de datos. Si el PLL dentro del circuito CDR no puede mantenerse enlazado por falta de transiciones, el receptor no puede garantizar sincronización sincrónica de bits de datos y ocurrirán errores de bits o falla de enlace. Usted logra CDR asegurándose de que los símbolos con transiciones frecuentes de bits se transmitan, lo que da como resultado que se agreguen bits de sobrecarga a los datos.

El equilibrio de DC también es importante para mantener funcionando un enlace serial. Si usted no regula la cantidad de equilibrio de DC, las señales podrían desviarse de sus niveles lógicos altos y bajos ideales y pueden ocurrir errores de bits. Usted garantiza el equilibrio de DC al equilibrar la cantidad estadística de 1 y 0 en los símbolos que se transmiten. En una señal DC equilibrada, el número de 0 y 1 transmitidos en el tiempo son estáticamente iguales en el tiempo.

Codificación 8b/10b

Un esquema común de codificación es 8b/10b. Por cada ocho bits de datos, se añaden dos bits adicionales para codificación. Estos dos bits adicionales proporcionan cuatro veces más representaciones de bits (símbolos) que ocho bits de datos. El codificador 8b/10b reduce sus muchas opciones de símbolos al elegir los símbolos predefinidos con la mayoría de las transiciones y el mejor equilibrio DC para mapear a palabras de datos específicas y símbolos de control. Almacena estos símbolos en tablas de consulta que se utilizan para codificar y decodificar los datos.

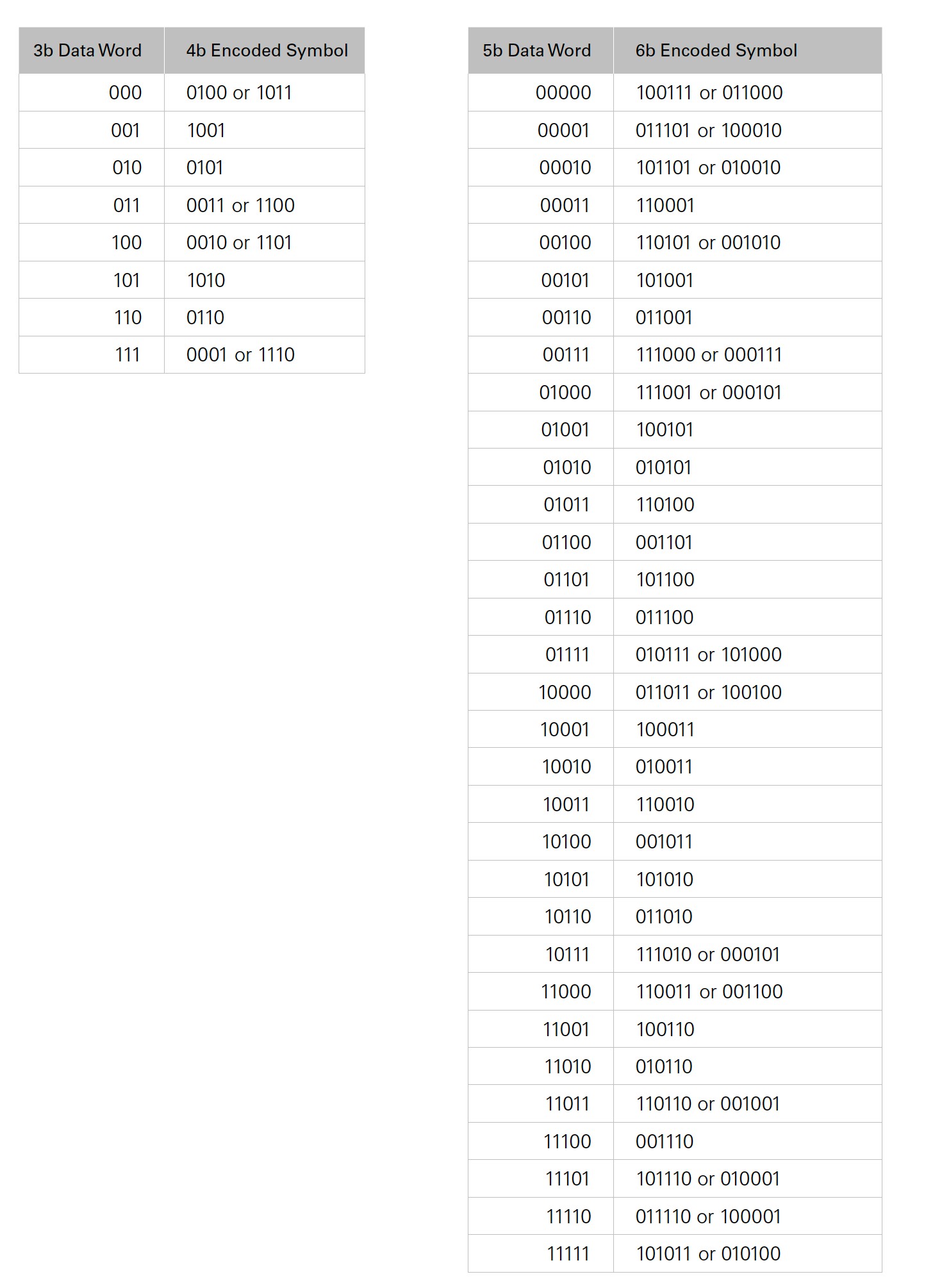

Cuando una palabra de datos de 8 bits está lista para ser codificada, el codificador separa la palabra de datos en cinco bits y tres bits y realiza codificación 5b/6b y 3b/4b por separado en la palabra de datos. Envía a la tabla 5b/6b los cinco bits menos significativos y los tres bits más significativos a la tabla 3b/4b.

Tabla 1: El codificador codifica palabras de datos 8b enviando los tres bits más significativos a una tabla 3b/4b y los cinco bits menos significativos a una tabla 5b/6b. Luego, el codificador los combina en base a la disparidad de ejecución para formar un símbolo 10b con transiciones frecuentes para los circuitos CDR.

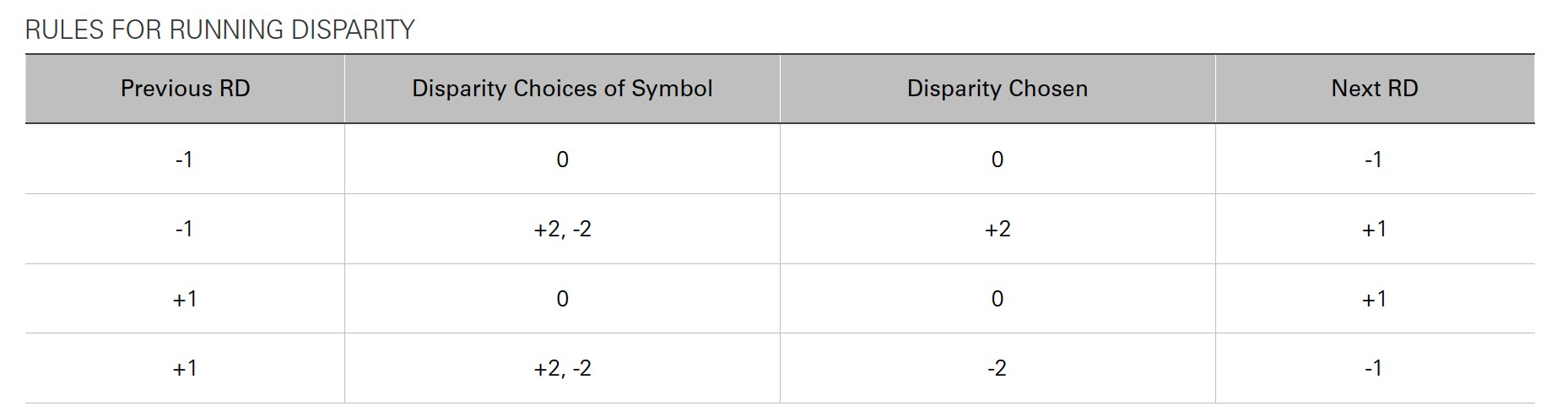

En una situación ideal, todos los símbolos tienen el mismo número de 0 y 1 para mantener el equilibrio de DC.. Pero este no es el caso de los símbolos en las tablas 5b/6b y 3b/4b, por lo que se implementaron reglas para tomar decisiones en base aun concepto conocido como "disparidad de ejecución". Esta es la diferencia acumulada entre el número de 1 y 0 que se han transmitido. No hay suficientes símbolos que tengan el mismo número de 1 y 0 para representar ocho bits, por lo que algunas palabras de datos son representadas con dos símbolos: un símbolo con más 0 que 1 y un símbolo con más 1 que 0. Por ejemplo, el símbolo en la tabla 3b/4b de 1101, también pueden ser representado como 0010. Al escoger la versión del símbolo a usar, el codificador siempre está tratando de equilibrar la disparidad de ejecución. La desigualdad de un símbolo 8b/10b completo siempre es 0, +2 o -2. La Tabla 2 muestra el proceso del codificador para decidir qué símbolo se debe usar.

Tabla 2: Las reglas para disparidad de ejecución determinan qué versión de la palabra de código se utiliza para garantizar el equilibrio de DC.

Por ejemplo, considere codificar la palabra de datos 10010001. Los tres bits más significativos (100) se envían a la tabla 3b/4b y los cinco bits menos significativos (10001) se envían a la tabla 5b/6b. Si esta es la primera palabra que se envía en la línea, el codificador asume una disparidad de -1; por lo tanto, este ejemplo asume que la disparidad de ejecución es -1. La porción 5b/6b no tiene elección, mientras que la porción 3b/4b decide si la disparidad es +2 o -2. Debido a que la disparidad de ejecución es -1, es elegido el código 3b/4b con disparidad +2 (1101). Cuando los códigos 3b/4b y 5b/6b son combinados, el símbolo total codificado es 1101100011. Después de que este símbolo es transmitido, la disparidad de ejecución ahora es +1 = -1 + 2.

Codificación 64b/66b

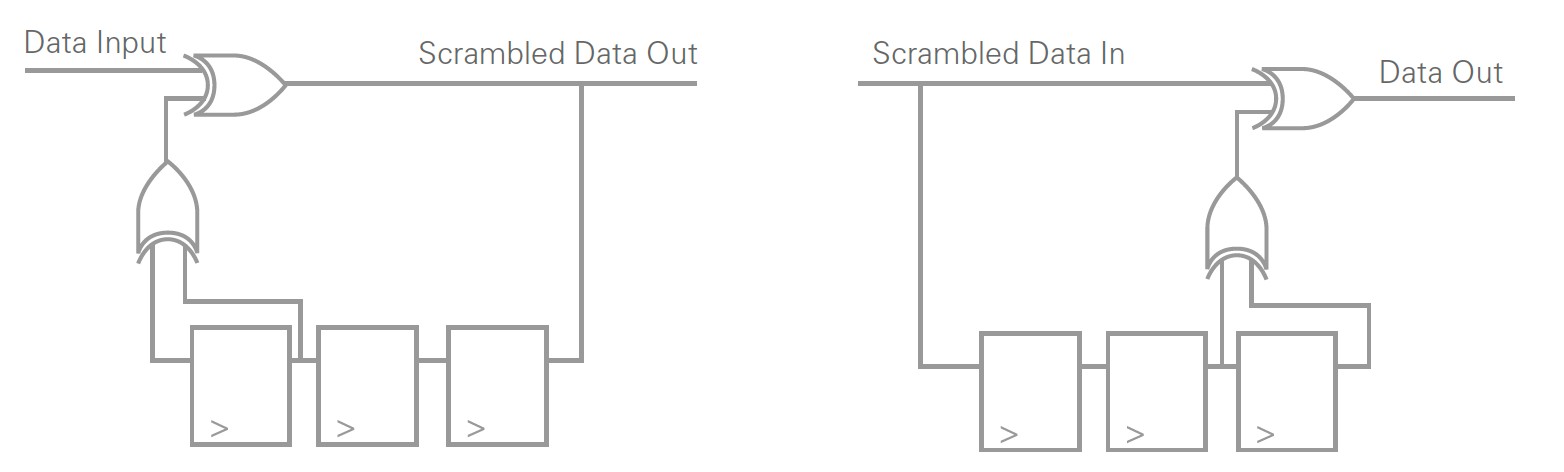

Utilizando un enfoque diferente al de la codificación 8b/10b, la codificación 64b/66b puede realizar tareas similares. En lugar de tablas de código, utiliza aleatorización. La aleatorización requiere un circuito de hardware que ofrece una alta probabilidad de varios 0 y 1 espaciados de manera uniforme. La aleatorización permite que los datos codificados aparezcan al azar con transiciones frecuentes, pero del lado del receptor aún se pueden descifrar.

Figura 7: Un circuito de aleatorización hace que los datos de salida aparezcan aleatorios y DC balanceado, pero los datos aún se pueden descifrar en el receptor. La aleatorización es un método alternativo para codificar datos con una tabla de consulta.

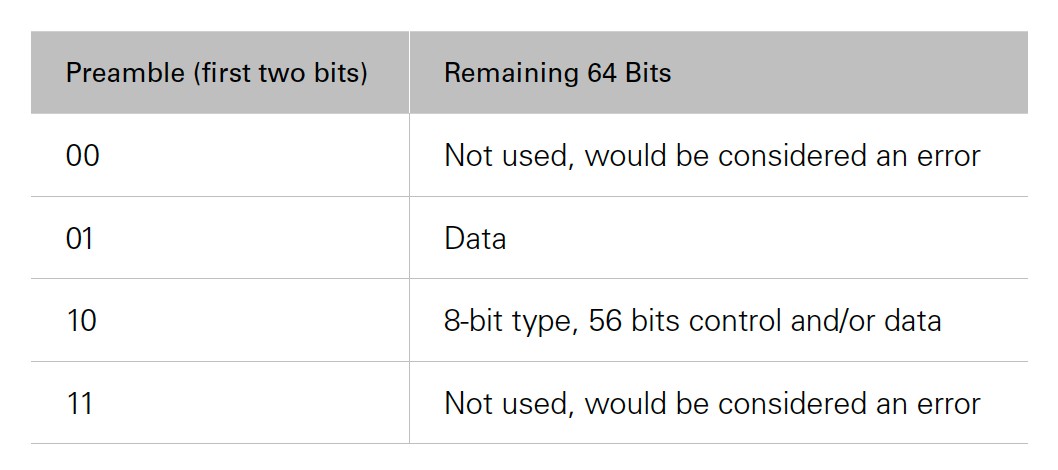

Los primeros dos de los 66 bits se consideran el preámbulo y proporcionan información sobre los 64 bits restantes. La ventaja principal de 64b/66b comparado con 8b/10b es la reducción de sobrecarga. La 64b/66b presenta un poco más del 3% de sobrecarga, mientras que la 8b/10b tiene un 20% de sobrecarga. Un inconveniente de la codificación 64b/66b es que no tiene límite en el equilibrio DC como lo hace la codificación 8b/10b. Aunque los circuitos de aleatorización han demostrado ser muy buenos para parecer aleatorios y tener un desequilibrio de DC estadísticamente insignificante, la codificación 64b/66b no está limitada como 8b/10b.

Tabla 3: Los primeros dos bits de un símbolo 64b/66b son considerados un preámbulo. El preámbulo proporciona información al decodificador sobre los 64 bits que siguen del preámbulo. Los significados del preámbulo de la Tabla 3 aplican a 10 Gigabit Ethernet.

64b/67b

Ciertos componentes electrónicos son demasiado sensibles al desfase de DC a lo largo del tiempo. Este puede ser el caso para el esquema de codificación 64b/66b. Podría no ser atractivo para los diseñadores porque el desfase de DC no está limitado. En estas situaciones, los ingenieros están detenidos con la sobrecarga más alta (20%) del esquema 8b/10b. El esquema 64b/67b añade un bit adicional de sobrecarga, lo que le permite limitar la disparidad de ejecución a ± 96.

El transmisor monitorea la disparidad de ejecución y calcula la nueva disparidad de palabras de código cifrado. Si la nueva palabra de código va a reducir el número de disparidad, transmite ese símbolo. Si la nueva palabra de código va a incrementar el número de disparidad, el codificador voltea los 64 bits cifrados (no hay necesidad de voltear el preámbulo pues su disparidad es cero). El bit adicional se conoce como el bit de inversión e informa al decodificador sobre si necesita invertir los datos o no. Esto permite que los electrónicos de chip que son sensibles al desfase de DC se beneficien de un esquema de codificación de baja sobrecarga que también muestra un desfase de DC limitado.

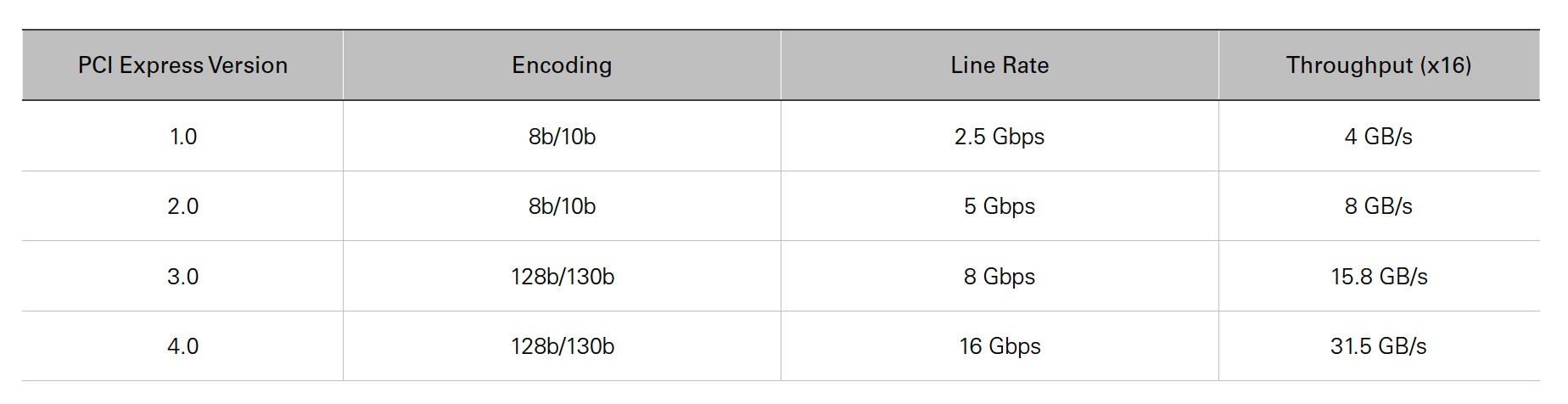

128b/130b

PCI Express 1.0 y 2.0 usan 8b/10b, mientras que PCI Express 3.0 y 4.0 dieron el salto a 128b/130b para tener un mayor rendimiento de datos con una velocidad de línea alcanzable. Piense en el esquema 128b/130b como 64b/66b con una carga útil duplicada y solo dos bits de preámbulo. La Tabla 4 muestra las especificaciones para PCI Express.

Tabla 4: Esta tabla muestra las especificaciones para las cuatro generaciones de PCI Express. PCI Express 3.0 y 4.0 cambiaron a 128b/130b para incrementar su rendimiento de datos manteniendo sus velocidades de línea a una velocidad más manejable.

Símbolos de control (caracteres-K)

Los símbolos de control, también conocidos como caracteres k al referirse a la codificación 8b/10b, son una función importante de los enlaces seriales de alta velocidad. Existen símbolos que se pueden diferenciar de los datos, permitiendo al receptor usarlos para diferentes responsabilidades de control, como alineamiento del límite de byte antes de la decodificación, técnicas de corrección de reloj y unión de canales para tener coherencia de los datos en múltiples líneas.

Alineación y detección de coma

Para que la decodificación funcione correctamente, el receptor necesita conocer los límites de palabras correctos de los datos codificados. El receptor escanea los datos entrantes para el carácter de control, también conocido como una coma cuando es usada para alineamiento en el esquema de 8b/10b. El carácter de control define el límite de los datos codificados. Una vez que el receptor ha identificado el carácter de alineamiento, tiene un concepto de límites de palabra para los datos codificados, por lo que los datos codificados se pueden enviar a la lógica de decodificación.

Caracteres de corrección de reloj

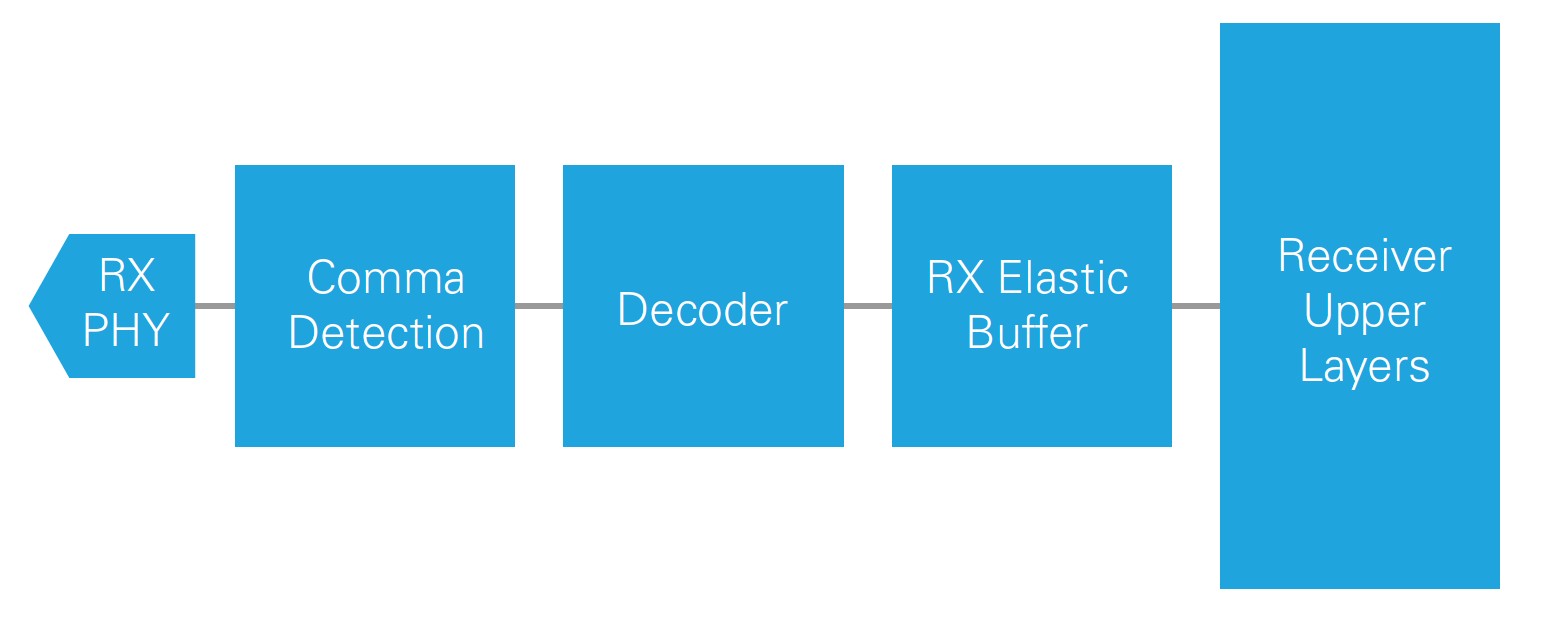

Se requiere corrección de reloj cada vez que el reloj de transmisión no está enlazado a la misma fuente que el reloj de recepción. Incluso si estos relojes están en la misma frecuencia nominal, se separan lentamente debido a pequeñas inexactitudes en la frecuencia del reloj. Tener un búfer de memoria first-in-first-out (FIFO), algunas veces conocido como un búfer elástico, le permite al receptor considerar diferencias menores de sincronización entre transmisor y receptor e implementa corrección de reloj.

Figura 8: Se requiere el búfer elástico RX entre las capas superiores del decodificador y receptor para implementar la corrección de reloj. Transfiere datos para prevenir errores debido a relojes no enlazados desfasándose uno de otro y permite la comunicación entre dos dispositivos sin compartir un reloj de referencia.

La lógica de corrección de reloj garantiza que el búfer elástico nunca sufra desbordamiento o escasez. Si el reloj de transmisión se está ejecutando ligeramente más rápido de como el reloj de recepción está leyendo desde el búfer elástico, puede ocurrir el desbordamiento si no se tienen técnicas de corrección de reloj. Si el reloj de transmisión se está ejecutando ligeramente más lento que la lógica de lectura en el receptor, puede ocurrir una escasez si no hay una corrección de reloj.

Se elije un carácter de control como un carácter de corrección de reloj. El transmisor envía este carácter de corrección de reloj intercalado periódicamente con datos reales y la frecuencia de ese carácter de corrección de reloj depende de las necesidades de corrección de reloj del diseño del hardware y de la aplicación. Si la lógica de corrección de reloj en el receptor detecta que el búfer elástico en el receptor va a escasear, la lógica de corrección del receptor puede insertar caracteres de corrección de reloj adicionales para garantizar que no ocurra escasez en el búfer. Si la lógica de corrección de reloj detecta que el búfer elástico se está llenando y está listo para desbordarse, la lógica puede descartar las secuencias de corrección de reloj en el búfer para que hacer más espacio para datos.

Unión de canales

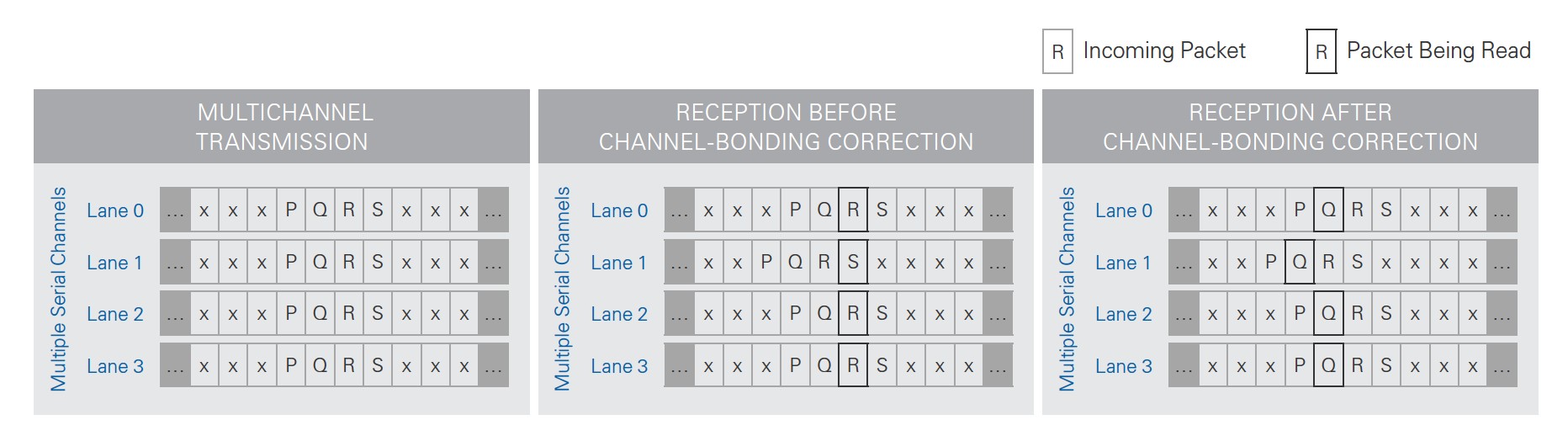

Si la velocidad de línea y el esquema de codificación no pueden brindar el rendimiento de datos que usted necesita en una sola línea serial, usted puede usar varias líneas. Como ejemplo, los estándares HDMI usan tres líneas de datos seriales para alcanzar su ancho de banda de datos completa. Al enviar datos entre múltiples líneas, los retrasos de propagación hacen que los datos lleguen en diferentes tiempos a cada línea de recepción en el receptor. Dependiendo de la aplicación, podría ser necesario alinear los datos en todas las líneas en el receptor, un proceso conocido como unión de canales. El búfer elástico en cada línea de recepción en el receptor utilizado para la corrección de reloj también se utiliza para la unión de canales.

Para lograr la unión de canales, usted debe elegir un carácter de control especial y reservarlo para la unión de canales. El enlace serial tiene una línea maestra y el resto son considerados esclavos. El maestro y todos los esclavos envían el carácter de unión de canales al mismo tiempo desde los transmisores. Cuando el receptor maestro ve la secuencia de unión de canales en cierta ubicación del búfer elástico, el receptor maestro pide a todos los esclavos encontrar sus secuencias de unión y ajusta los punteros de lectura de todos los búferes elásticos al desfase de la ubicación de la secuencia de unión de canales. Debido a que cada línea de datos tiene su propio desfase para su propio búfer elástico, el receptor puede leer desde diferentes ubicaciones de cada búfer elástico, lo que resulta en una lectura de datos alineados.

Figura 9: La unión de canales cambia los punteros de lectura del búfer elástico en cada línea de recepción para permitir que el receptor lea datos síncronos en múltiples líneas de datos.

Caracteres inactivos

Otro caso de uso importante para los caracteres de control es el carácter inactivo. Para que el reloj y la recuperación de datos permanezcan enlazados en fase, el transmisor debe enviar bits continuamente. Cuando no tiene datos para enviar, debe enviar un carácter inactivo. Este es otro carácter de control determinado por el protocolo y el receptor sabe que ese carácter no tiene datos verdaderos.

Capas superiores adicionales

Las capas superiores adicionales se encuentran encima de la capa de enlace de datos para ayudarlo a adaptar la comunicación de acuerdo a sus necesidades específicas. Algunos protocolos tienen estándares específicos para características de la capa superior y otros protocolos lo dejan en sus manos. Las personalizaciones de comunicación comunes incluyen verificación/corrección de errores, información del encabezado para comunicación basada en paquete o incluso información del estado del enlace.

Las capas por encima de la capa de enlace de datos y la capa física son las capas más comúnmente personalizadas para las necesidades específicas de la aplicación. Algunos ejemplos de las características comunes de la capa superior son detección y corrección de errores a través de comprobación de redundancia cíclica (CRC) y corrección de errores hacia adelante (FEC). Como una solución para eficiencia de la transferencia de datos, puede utilizar esquemas para detectar o corregir errores. CRC implementa reglas para detectar errores de bits en la transmisión, pero no puede corregir los errores. Usted puede personalizar la aplicación para volver a solicitar datos. FEC, por el contrario, contiene información adicional de corrección de errores en los datos transmitidos que pueden permitir al receptor recuperarse de una cantidad limitada de errores de bits. Esto es útil para canales ruidosos o velocidades de comunicación tan altas que los errores de bits debidos a la integridad de la señal son más comunes. Incluir FEC es una decisión de diseño que sacrifica la eficiencia de la velocidad de datos por requisitos de integridad de señal más condescendientes.

Conclusiones

Usted debe superar muchos desafíos en varias capas del enlace serial de alta velocidad para comunicarse con éxito. Tener conocimiento de los diferentes conceptos en cada nivel le ayuda a implementar y probar diferentes capas. Para que cualquier capa funcione, las capas debajo de ella necesitan estar funcionando correctamente. Al utilizar una de las muchas especificaciones definidas para las capas físicas y de enlace de datos, usted no tiene que determinar los detalles de bajo nivel por su cuenta. Otro beneficio de usar una capa física y de enlace de datos estándar es el protocolo de internet (IP) que implementa todos estos detalles de bajo nivel para usted. Un gran ejemplo de esto es el Protocolo Xilinx Aurora, un IP gratuito que implementa un protocolo de capa de enlace de datos para comunicación serial punto a punto. Esto le ayuda a abstraer los pequeños detalles como corrección de reloj, unión de canales, carácter inactivo, codificación/decodificación y más, para que usted pueda enfocarse en las capas superiores específicas de la aplicación.

Con los beneficios de menor tamaño y potencia, además de mayor rendimiento, los enlaces seriales de alta velocidad se están volviendo populares rápidamente. La industria de las comunicaciones está mejorando continuamente las tecnologías seriales de alta velocidad para alcanzar velocidades de línea más rápidas y habilitar el mundo de big data.