Häufig gestellte Fragen (FAQ) zu NI Multifunktions RIO

Inhalt

- Was ist die RIO-Technologie?

- Was sind die neuen Multifunktions-RIO-Geräte?

- Wie unterscheiden sich die neuen Geräte der R-Serie von Geräten der vorherigen Generation?

- Vergleich von FPGAs auf NI-FPGA-Produkten

- Wie entscheide ich, welches FPGA für meine Anwendung geeignet ist?

- Funktioniert mein Virtex-II-Programm auf einem Virtex-5 oder Kintex-7?

- Muss ich mich mit VHDL auskennen, um LabVIEW FPGA zu verwenden?

- Benötige ich das LabVIEW FPGA Module zur Programmierung von Geräten der R-Serie?

- Kann ich mein Gerät der R-Serie in C/C++ programmieren?

- Wie unterscheidet sich die R-Serie von anderen Datenerfassungsfamilien?

- Kann ich Geräte der R-Serie mit NI-DAQmx, NI-DAQmx Base oder dem NI Measurement Hardware DDK programmieren?

- Was sind die internen Verarbeitungsfunktionen der R-Serie?

- Kann ich mit einem Gerät der R-Serie eine simultane analoge Ein- und Ausgabe erzielen?

- Zusätzliche Ressourcen

Was ist die RIO-Technologie?

Rekonfigurierbare I/O-Technologie (RIO) von National Instruments ermöglicht die Erstellung benutzerdefinierter Messhardware mithilfe rekonfigurierbarer FPGA-Chips und der grafischen Entwicklungsumgebung NI LabVIEW. Multifunktions-RIO-Geräte der R-Serie bieten die beste Kombination aus Wert und Leistung, indem sie diese FPGA-Technologie mit acht Analogeingängen, acht Analogausgängen und bis zu 96 Digital-I/O-Leitungen in einem Gerät integrieren, das auf Standard-PC-Formfaktoren wie PCI, PCI Express, PXI/CompactPCI und USB angeboten wird. Mithilfe des LabVIEW FPGA Module können Anwender ihre eigene Hardware so konfigurieren, dass benutzerdefinierte Datenerfassung, Regelkreise mit hohen Geschwindigkeiten, digitale Kommunikationsprotokolle, Sensorsimulationen sowie geräteeigene Signalverarbeitung möglich sind, ohne dass detaillierte Kenntnisse von Hardwarebeschreibungssprachen erforderlich wären.

Abbildung 1. Geräte der R-Serie werden auf Standard-PC-Formfaktoren wie PCI, PCI Express, PXI/CompactPCI und USB angeboten.

Was sind die neuen Multifunktions-RIO-Geräte?

Die neuesten Multifunktions-RIO-Geräte finden Sie auf den folgenden Shop-Seiten:

Wie unterscheiden sich die neuen Geräte der R-Serie von Geräten der vorherigen Generation?

Die neuen Geräte der R-Serie sind mit leistungsstarken Kintex-7-FPGAs ausgestattet, die verbesserte Optimierungsfunktionen bieten, um eine schnellere Code-Ausführung und mehr LabVIEW-Code-Kapazität als Geräte der vorherigen Generation der R-Serie zu erzielen. Die neuen Kintex-7-FPGAs sind besonders für die USB-Hardware der R-Serie geeignet. Diese Produkte bieten die Kapazität und Leistungsfähigkeit der High-End-FPGAs der letzten Generation, benötigen jedoch nur halb so viel Energie. Aufgrund dieses erheblich reduzierten Energieverbrauchs können bis zu zehnmal so viele DSP-Slices (Digital Signal Processing) pro Gerät realisiert werden wie bei der vorherigen Generation von Modulen der R-Serie. Mithilfe dieser zusätzlichen Ressourcen für Logik und DSP können durch die umfangreichere Nutzung von Signalverarbeitungs- und Echtzeitanalysefunktionen komplexere Algorithmen implementiert sowie die wachsenden I/O-Datenraten und die Vielschichtigkeit heutiger Anwendungen bewältigt werden. Weitere Informationen zu Kintex-7-FPGAs finden Sie unter [Vorteile von FPGA-Modulen der Xilinx-7-Serie].

Darüber hinaus können die neuen USB-785xR-Geräte von NI mit einer Sample-Rate von bis zu 1 M/s auf allen acht analogen Eingangskanälen mit einer Auflösung von 16 Bit und einer wählbaren Verstärkungsauflösung von ±10 V, ±5 V, ±2 V und ±1 V abtasten. Bei der parallelen Ausführung auf FPGA-Basis müssen mehrere Steuerschleifen nicht um die Prozessorbandbreite konkurrieren. Schnellere analoge Eingangsraten verbessern auch die Genauigkeit des Analog-Triggers und die Fähigkeit zur Frequenzmessung. Die neuen NI USB-785xR-Geräte unterstützen außerdem nativ die Festkomma-I/O, wodurch Sie direkt mit technischen Einheiten im FPGA arbeiten können.

Schließlich verfügen die neuen Geräte der R-Serie über schnellere digitale I/O-Kanäle, die mit Taktfrequenzen von bis zu 80 MHz auslösen können. Darüber hinaus können Sie die Spannungspegel der digitalen I/O-Leitungen direkt vom LabVIEW-FPGA aus auswählen. Die verfügbaren Logikpegel sind 3,3 V, 2,5 V, 1,8 V, 1,5 V und 1,2 V.

Vergleich von FPGAs auf NI-FPGA-Produkten

Die Anzahl der Gates war traditionell eine Möglichkeit, FPGA-Chips mit ASIC-Technologie zu vergleichen, aber sie beschreibt nicht wirklich die Anzahl der einzelnen Komponenten in einem FPGA. Dies ist einer der Gründe, warum sich Xilinx von der Angabe der Anzahl der Gates in einem FPGA entfernt hat. Stattdessen vergleicht man nunmehr einige unterschiedliche Komponenten, darunter Flipflops, Zuordnungstabellen (LUTs), DSP-Logikblöcke und den verfügbaren Blockspeicher. Weitere Informationen finden Sie in den Tabellen im Handbuch Logikblöcke auf einem FPGA-Chip.

Wie entscheide ich, welches FPGA für meine Anwendung geeignet ist?

Leider ist es schwierig zu bestimmen, ob eine Anwendung oder ein Programm einen größeren oder kleineren FPGA erfordert. Mit dem LabVIEW-FPGA-Modul und dem NI-RIO-Treiber können Sie Blockdiagramme kompilieren, ohne überhaupt Hardware zu haben. Der beste Weg, um zu sehen, wie viele Ressourcen Sie benötigen, ist es, es auszuprobieren.

Bei der Entscheidung, welcher FPGA für Ihre Anwendung geeignet ist, können Sie folgende allgemeine Richtlinien anwenden: Für eine Anwendung, die einfache Timing-, Trigger- und Synchronisationsfunktionen auf dem FPGA durchführt, können Sie einen kleineren FPGA verwenden. Wenn die Anwendung Timing, Triggering und Synchronisation sowie zusätzliche Signalverarbeitung auf dem FPGA (Steuerung, digitale Filterung, komplexe analoge Triggerung) umfasst, benötigen Sie einen größeren FPGA, der über mehr Ressourcen zur Implementierung dieser Operationen verfügt.

Funktioniert mein Virtex-II-Programm auf einem Virtex-5 oder Kintex-7?

Im Allgemeinen sollte ein für ein Virtex-II-1M-Gate-FPGA kompiliertes Programm auch für ein Virtex-5 LX30 oder größeres Programm kompiliert werden, und ein für ein Virtex-II-3M-Gate-FPGA kompiliertes Programm sollte auch für ein Virtex-5 LX50 oder größeres Programm kompiliert werden. Aufgrund von Architekturunterschieden zwischen den beiden FPGA-Familien gibt dafür jedoch keine Garantien. Die einzige Möglichkeit, zu sehen, ob ein Programm zwischen den beiden Familien migriert werden kann, besteht darin, es auszuprobieren. Mit dem LabVIEW FPGA Module und dem NI-RIO-Treiber können Sie Blockdiagramme kompilieren, ohne überhaupt Hardware zu haben.

Muss ich mich mit VHDL auskennen, um LabVIEW FPGA zu verwenden?

Nein. Mit dem LabVIEW FPGA Module können Sie grafischen Programmcode direkt von LabVIEW auf dem FPGA von Geräten der R-Serie synthetisieren. Wenn Sie wissen, wie LabVIEW grafische Blockdiagramme in VHDL kompiliert, können Sie bei der Optimierung bestimmte Kompromisse erkennen. Für LabVIEW sind jedoch weder FPGA- noch VHDL-Kenntnisse erforderlich. LabVIEW eignet sich ideal für Ingenieure, die die von der FPGA-Technologie gebotene Hardwareanpassung benötigen, aber nicht mit Low-Level-Hardwarebeschreibungssprachen wie VHDL oder Verilog vertraut sind.

Benötige ich das LabVIEW FPGA Module zur Programmierung von Geräten der R-Serie?

Ja, zur Programmierung von Geräten der R-Serie müssen Sie das LabVIEW FPGA Module verwenden. Wenn Sie jedoch über vorhandene VHDL-IP-Kerne oder anderen VHDL-Code verfügen, den Sie verwenden möchten, können Sie VHDL mithilfe des HDL-Schnittstellenknotens in ein LabVIEW-Blockdiagramm integrieren.

Lesen Sie diesen Anwendungshinweis, um zu erfahren, wie VHDL in ein LabVIEW-Blockdiagramm integriert wird.

Kann ich mein Gerät der R-Serie in C/C++ programmieren?

Mit der FPGA-Interface-C-API können Sie den Echtzeitprozessor auf FPGA-basierter Hardware von NI mithilfe von C-Tools wie NI LabWindowsTM/CVI und Microsoft Visual Studio programmieren und eine Schnittstelle zum LabVIEW-FPGA-Code auf dem FPGA herstellen. Mit anderen Worten, der auf Ihrem Host-Computer ausgeführte Code kann in C/C++ oder LabVIEW geschrieben werden, während der tatsächlich auf dem FPGA bereitgestellte Code in LabVIEW FPGA geschrieben werden muss.

Erfahren Sie mehr über die FPGA-Interface-C-API.

Wie unterscheidet sich die R-Serie von anderen Datenerfassungsfamilien?

Statt eines festen ASICs zur Steuerung der Gerätefunktionen bieten DAQ-Geräte der R-Serie einen anwenderprogrammierbaren FPGA-Chip für die geräteeigene Verarbeitung und den flexiblen I/O-Betrieb. Die Geräte der R-Serie umfassen einen dedizierten A/D-Wandler pro Kanal für unabhängige Timing- und Triggerfunktionen. Dieser ermöglicht spezielle Funktionen, wie z. B. unterschiedliche Abtastraten und Triggerung einzelner Kanäle, die normalerweise nicht in Datenerfassungshardware möglich sind. Sie können die hardwaregetaktete digitale I/O von Geräten der R-Serie als Zähler, PWM-Kanäle, flexible Encoder oder Leitungen für digitale Kommunikationsprotokolle definieren.

Kann ich Geräte der R-Serie mit NI-DAQmx, NI-DAQmx Base oder dem NI Measurement Hardware DDK programmieren?

Alle Multifunktions-RIO-Geräte der R-Serie verwenden NI-RIO-Treibersoftware. Sie sind nicht mit NI-DAQmx oder NI-DAQmx Base kompatibel. Das NI Measurement Hardware DDK (Driver Development Kit) bietet jedoch Unterstützung für die Entwicklung benutzerdefinierter Treiber über die Programmierung auf Registerebene. Nachdem Sie eine LabVIEW-FPGA-Anwendung kompiliert und auf ein Zielsystem der R-Serie heruntergeladen haben, stellt das NI Measurement Hardware DDK die Dokumentation für die Host-Anwendung bereit, um mit den Registern auf dem FPGA zu arbeiten.

Was sind die internen Verarbeitungsfunktionen der R-Serie?

Das LabVIEW FPGA Module enthält eine Signalverarbeitungspalette mit zahlreichen Funktionen wie:

- PID-Regelung

- Butterworth-Filter (Hochpass und Tiefpass)

- Kerbfilter

- Messung der Periodendauer analoger Signale

- DC- und Effektivwertmessung

Kann ich mit einem Gerät der R-Serie eine simultane analoge Ein- und Ausgabe erzielen?

Ja. Alle Multifunktionsgeräte der R-Serie verfügen über dedizierte A/D-Wandler und Digital-Analog-Wandler (DACs) an jedem analogen Ein- und Ausgangskanal, so dass alle Kanäle gleichzeitig oder mit unterschiedlichen Raten abgetastet/aktualisiert werden können. Mit unabhängigen A/D-Wandlern können Sie jeden Kanal des Geräts mit der maximalen Rate (bis zu 1 MS/s) abtasten. Sie können die unabhängigen D/A-Wandler so programmieren, dass die analoge Ausgangskanäle mit Raten von bis zu 1 MS/s aktualisiert werden.

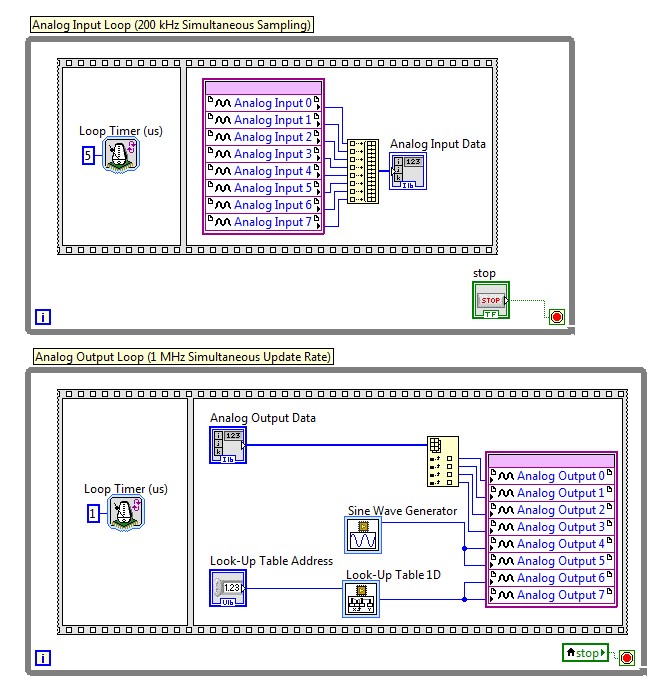

Das LabVIEW-FPGA-Blockdiagramm in Abbildung 2 zeigt, wie einfach es ist, auf FPGAs der R-Serie gleichzeitig analoge Ein- und Ausgänge zu implementieren. Durch Verwendung eines LabVIEW-FPGA-Knotens für analoge I/O, der von allen acht Kanälen des Geräts der R-Serie in derselben While-Schleife gelesen wird, sammelt das Programm Samples von allen acht Kanälen gleichzeitig. Die untere parallele Schleife verwendet den LabVIEW-FPGA-I/O-Knoten für die Analogausgabe und aktualisiert alle acht analogen Ausgangskanäle mit 1 MS/s.

Abbildung 2: Simultane Analogeingabe/Analogausgabe mit der R-Serie und dem LabVIEW FPGA