Einsatz der SLSC-Architektur zur Erweiterung des Signalpfads eines Prüfsystems um zusätzliche Elemente

Inhalt

- Einführung

- Verfolgen des Signalwegs vom Ausgang zum Eingang

- Betriebliche Theorie

- Überblick über die SLSC-Architektur und das Modul Development Kit

- Beschreibung der Hardwaresystemkomponenten

- Software

- Fazit

- Anhang 1: Hardwaresystemkomponenten

- Anhang 2: Quellen

Einführung

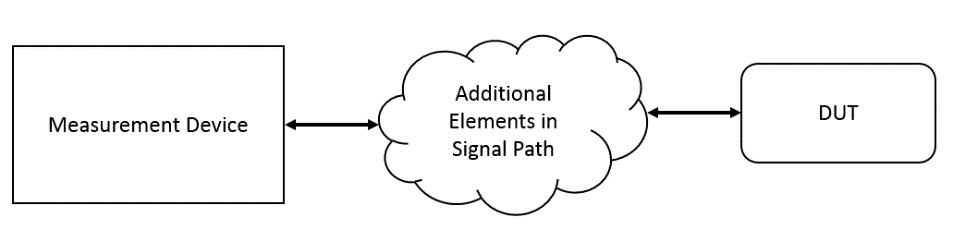

Bei der Erstellung von Prüfsystemen werden häufig für den Signalpfad vom Prüfling zum Messgerät zusätzliche Elemente zur benutzerdefinierten Signalkonditionierung, zum Laden und Schalten benötigt. Vor diesem Hintergrund hat NI die NI Switch Load and Signal Conditioning-Architektur (SLSC) entwickelt. In diesem Dokument wird dargestellt, wie NI SLSC verwendet werden kann, um den Signalpfad in einem typischen Prüfsystem um zusätzliche Elemente zu erweitern.

Als Anwendungsbeispiel werden wir ein elektronisches Steuergerät (ECU) mit einem Pulsbreitenmodulationssignal (PWM) anregen, wie es üblicherweise in elektronischen Steuergeräten (ECUs) verwendet wird, und dessen Reaktion messen. Da viele Steuergeräte höhere Spannungspegel benötigen, fügen wir zusätzliche Elemente hinzu, um Level-Shifting durchzuführen und ein Signal zu erzeugen und zu messen, das auf eine externe Stromversorgung wie eine Autobatterie referenziert ist.

Außerdem fügen wir ein Relais hinzu, um einen Fehler in den Signalpfad einzufügen, der eine nicht ausführbare Verbindung im ECU-Kabelbaum simuliert.

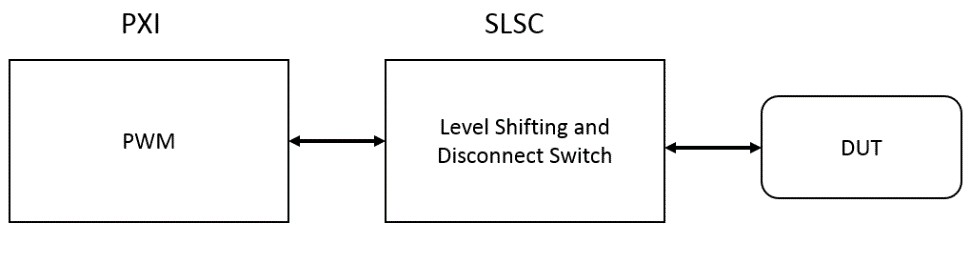

Im System wird ein FPGA-Board der NI PXI R-Serie verwendet, um das digitale PWM-Signal in einem PXI-Chassis zu erzeugen und zu messen. Anschließend werden Spannungen skaliert und das Schaltmodul im SLSC-Chassis hinzugefügt.

Der Einfachheit halber werden wir in diesem Beitrag kein echtes Steuergerät verwenden. Bei unserem Prüfling handelt es sich in diesem Fall um einen Anschlussblock, um den das Kabel gewickelt wird und der einen der digitalen Eingänge der R-Serie verwendet, um das vom digitalen Ausgang erzeugte PWM-Signal zu messen.

Verfolgen des Signalwegs vom Ausgang zum Eingang

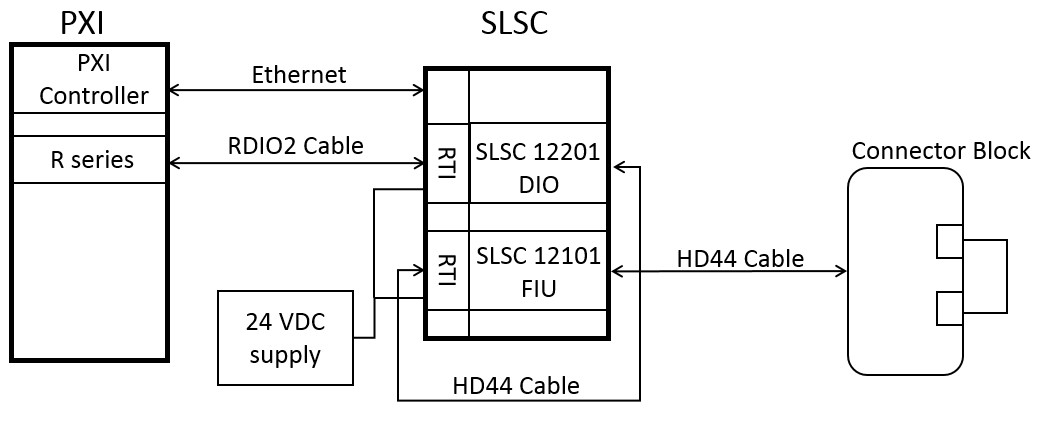

Das folgende Diagramm stellt den Signalweg dar, der vom PXI-System durch den SLSC zum Anschlussblock führt, wo das Signal umgelenkt und durch den SLSC zurück zum PXI-System geleitet wird.

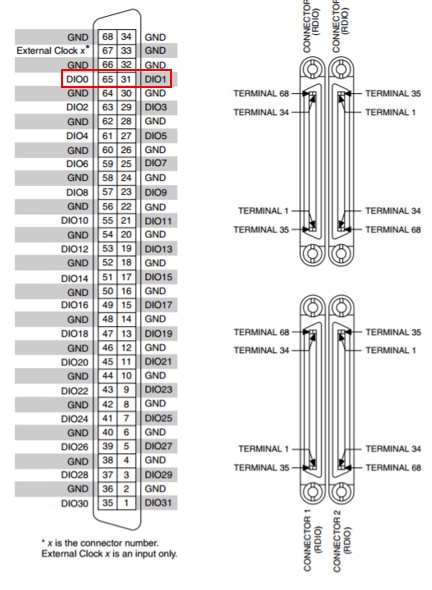

Das PXIe-7822R-Modul wird über ein standardmäßiges SHC68-C68-RDIO2-Kabel an ein RTI-12301 angeschlossen. Der RTI-12301 gibt die Signale für das SLSC-12201-Modul aus. Der SLSC-12201 wird verwendet, um die Signale in Bezug auf eine externe Referenzquelle zu skalieren. In diesem Fall verwenden wir eine Spannung von 24 V, aber in der realen Welt könnte diese Spannung der Batteriespannung eines Kfz-Steuergeräts oder einer Flugzeug-LRU entsprechen. Das Signal wird über ein HD 44-Kabel von der Vorderseite des SLSC zur Rückseite geführt und an einen RTI-12305 angeschlossen. Das RTI-12305 unterbricht die Signale für das SLSC-12101, das als Schaltmodul verwendet wird, um eine nicht ausführbare Verbindung im Kabelbaum zu simulieren.

In den folgenden Bildern wird die Vorder- und Rückseite des Aufbaus dargestellt, der zusätzliche PXI- und SLSC-Module enthält, die in dieser Anwendung nicht verwendet werden. Das Wrap-Back-Kabel, die externe Referenz und das Ethernet-Kabel sind auf diesen Bildern als nicht verbunden dargestellt. Im folgenden Abschnitt wird der Signalpfad genauer beschrieben und der Weg vom PWM-Ausgang zum PWM-Eingang dargestellt.

Bild 4. Rückseitige Ansicht des SLSC

Bild 5. Vorderseitige Ansicht des SLSC und eines PXI-Systems

Betriebliche Theorie

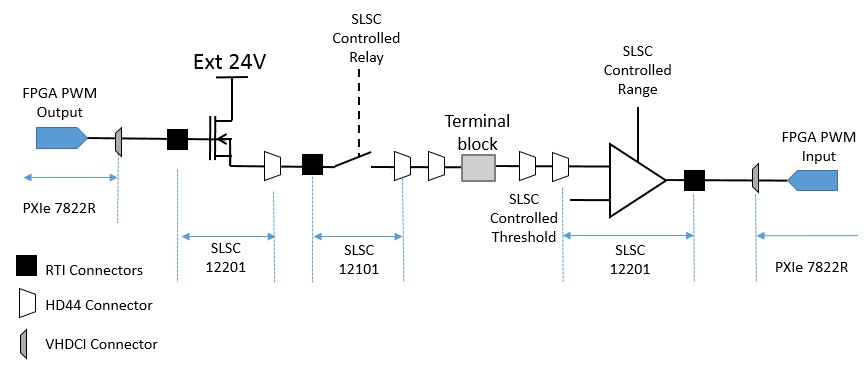

Das PWM-Signal wird im FPGA erzeugt, der FPGA-Programmcode ist im Softwareteil dargestellt. Der Ausgangspin des FPGAs ist am VHDCI-Anschluss auf dem Frontpanel des PXIe-7822R zugänglich. Es handelt sich um ein 3,3-Volt-Signal. Die Impulsfolge wird über ein SHC68-C68-RDIO2-VHDCI-Kabel an das RTI-12301 Rear Transition Interface auf dem SLSC-Chassis übertragen.

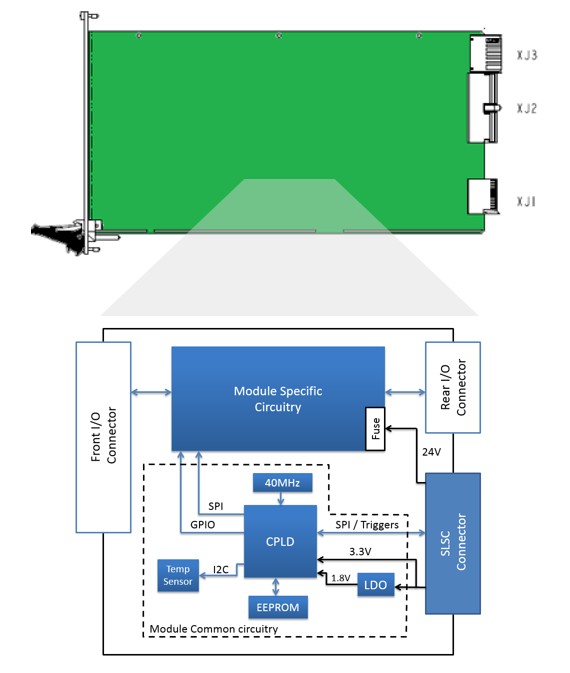

Das SLSC Module Development Kit spezifiziert eine Standardmethode zur Verteilung der Signale vom RTI an das SLSC-Modul.

Die Impulsfolge wird dann durch das Modul SLSC-12201 verstärkt, das sie auf der Grundlage des externen Vsup in Spannungen zwischen 5 V und 33 V umwandeln kann. Das SLSC-12201 Modul wird über den Ethernet-Port mithilfe der SLSC-API programmiert und kann in verschiedenen Modi betrieben werden. In diesem Fall wurde der Ausgang so programmiert, dass er als Sourcing-Ausgang arbeitet und eine externe Referenz verwendet, die an den Vsupp-Pin des RTI-12301 angeschlossen ist. In diesem Beispiel verwenden wir eine externe Gleichstromquelle mit 24 V.

Das Signal arbeitet mit Pulsbreitenmodulation (PWM) in einem Bereich zwischen 0 V und 24 V. Dieses Ausgangssignal ist am HD44-Anschluss an der Vorderseite des SLSC-12201-Moduls verfügbar. Das Signal wird mit einem 1:1-HD44-Kabel zum RTI-12305 gewickelt und einem Prototypenerstellungsmodul SLSC-12101 zur Verfügung gestellt. In diesem Modul haben wir ein Relais platziert, das über einen der softwaregesteuerten Pins auf dem SLSC 12101 Controller (CPLD) gesteuert wird.

Wenn das Relais aktiviert ist, kann das Signal durch das Relais geleitet werden und steht auf dem HD 44-Anschluss an der Vorderseite des SLSC-12101-Moduls zur Verfügung. Das Signal wird über ein 1:1-HD-44-Kabel zu einem Anschlussblock übertragen, wo es auf den Eingang gewickelt wird.

Der Rückweg verläuft ähnlich. Es gibt jedoch kein Relais auf dem SLSC-12101-Modul, das Signal wird einfach durchverbunden und an das SLSC-12201 weitergeleitet, das im Eingangsmodus und mit einem Schwellenwert von 12 V konfiguriert ist, bevor es auf einen Wert zurückskaliert wird, der vom FPGA gelesen werden kann.

Überblick über die SLSC-Architektur und das Modul Development Kit

SLSC-Architektur

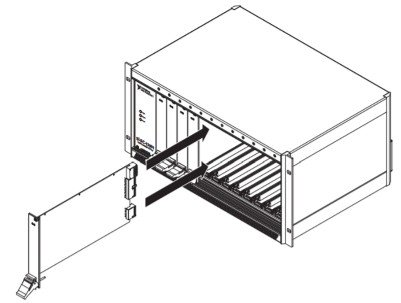

SLSC ist eine modulare Architektur, die als Ergänzung zu den NI-Hardwareplattformen PXI und C-Serie konzipiert wurde. Sie soll Kunden und Partnern die Erstellung benutzerdefinierter Schaltungskarten für Prüfsysteme erleichtern, die sowohl hardware- als auch softwareseitig problemlos miteinander verbunden werden können.

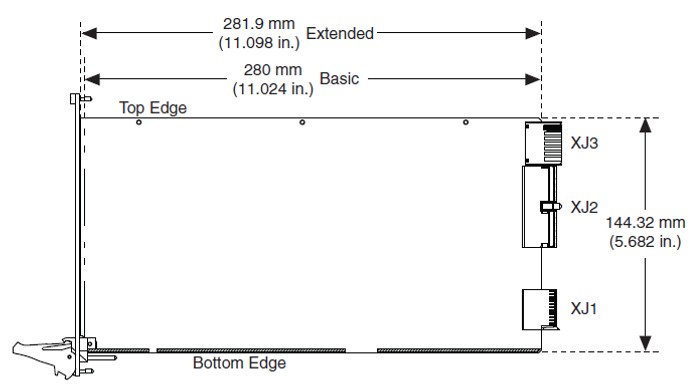

Die SLSC-Architektur besteht aus drei Komponenten: dem Chassis, dem Modul und dem Rear Transition Interface (RTI). Einzelheiten zum Chassis entnehmen Sie bitte dem Erste-Schritte-Handbuch. Wie in den nachstehenden Diagrammen dargestellt, sind die Module 144,32 mm hoch (4U) und 281,9 mm tief, mit drei Anschlüssen auf der Rückseite (XJ1, XJ2 und XJ3). Der XJ1-Anschluss wird für die Modulkommunikation mittels der SLSC-Treiber-API verwendet, der XJ2-Anschluss dient als Signalschnittstelle und der XJ3-Anschluss wird für Hochleistungsverbindungen verwendet.

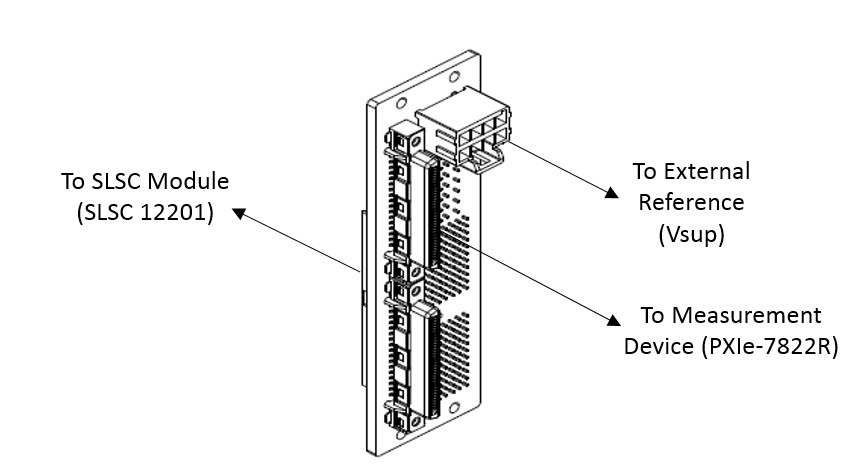

Das Rear Transition Interface (RTI) ermöglicht den Anschluss der SLSC-Module an die Messhardware von NI. Anwendungen können aus einer Vielzahl von RTIs von NI und Drittanbietern auswählen oder ihre eigenen entwerfen. Durch die Entwicklung eigener RTIs kann der Systementwickler die Verkabelung und die Punkt-zu-Punkt-Verbindungen in Systemen reduzieren.

Im folgenden Diagramm sind die Anschlüsse des RTI an die externe Referenz, das Messgerät und an das SLSC-12201-Modul dargestellt.

SLSC Module Development Kit

Das SLSC Module Development Kit (MDK) bietet detaillierte Designvorgaben für Entwickler, um die Systeminteroperabilität mit anderen Modulen und Produkten des Ökosystems zu erreichen. Um Module erstellen zu können, benötigt der Benutzer ein gültiges MDK-Kit von NI. Weitere Informationen zur Beschaffung des MDK erhalten Sie bei NI.

Beschreibung der Hardwaresystemkomponenten

PXIe-Chassis mit LabVIEW 2015 und PXIe-7822R

Das PXIe-7822R ist ein rekonfigurierbares I/O-Modul (RIO), das über einen anwenderprogrammierbaren FPGA für die integrierte Verarbeitung und flexible I/O-Handhabung verfügt. Mithilfe von LabVIEW FPGA lassen sich die Digitalkanäle individuell als Eingänge, Ausgänge, Counter/Timer, flexible Encoder-Eingänge, mit PWM oder speziellen Kommunikationsprotokollen konfigurieren. Anwender können darüber hinaus benutzerdefinierte Entscheidungslogik auf Board-Ebene programmieren, die mit hardwaregetakteter Geschwindigkeit und Zuverlässigkeit ausgeführt wird. In diesem Projekt verwenden wir DIO0 als PWM-Ausgang und DIO1 als PWM-Eingang.

SLSC-12201

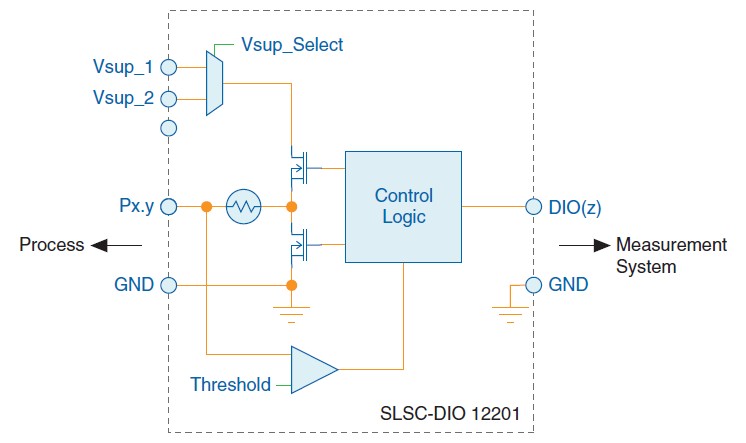

Das SLSC-12201 ist ein Modul zur Aufbereitung von Digitalsignalen, das für den Einsatz mit digitalen Eingangs- und Ausgangsgeräten (DIO) von NI entwickelt wurde. Im Folgenden sehen Sie ein Blockdiagramm und ein Bild des Moduls.

Das Modul ist über den SLSC-Bus entweder als Ausgang oder als Eingang konfigurierbar. Als Ausgang ist es in der Lage, Digitalsignale auf der Grundlage einer von zwei externen Referenzen (Vsup_x) zu verstärken. Die Ausgangsschaltung kann außerdem so programmiert werden, dass sie in 3 Betriebsarten arbeitet: „push“, „pull“ oder „push and pull“.

Als Eingang ist das Modul standardmäßig auf Pull-down eingestellt, es ist jedoch möglich, einen programmierbaren Pull-up zu konfigurieren. Der Schwellenwert des Eingangssignals kann so programmiert werden, dass er als Standard-5-V-TTL-Eingang oder als erweiterter Bereich mit programmierbarem Schwellenwert arbeitet.

Die externe Referenz (Vsup_x) kann auf eine von zwei Bänken mit je 8 Kanälen programmiert werden.

Für diese Konfiguration verwenden wir Vsup_1, das am JR1-Anschluss des RTI-12301-Anschlusses mit 24 V verbunden ist.

In diesem Projekt verwenden wir P0.0 als skalierten PWM-Ausgang und P0.1 als skalierten PWM-Eingang.

RTI-12301

Mit dem RTI-12301 werden die Signale des PXIe-7822R-Moduls mithilfe eines standardmäßigen SHC68-C68-RDIO2-Kabels dem SLSC-12201-Modul zugeordnet. Damit wird der DIO0 des PXIe-7822R dem P0.0 des SLSC-12201-Moduls und der DIO1 dem P0.1 zugeordnet.

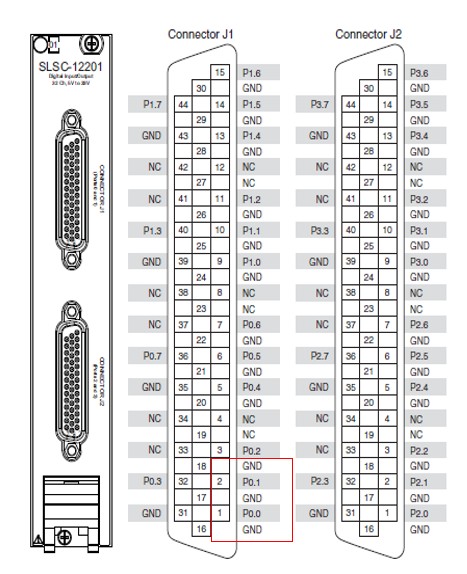

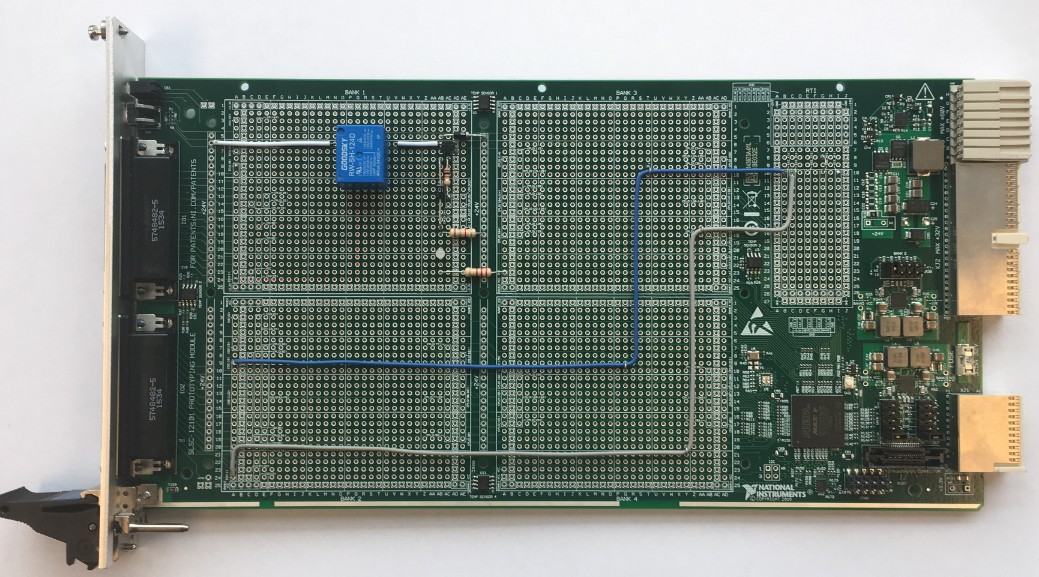

SLSC-12101

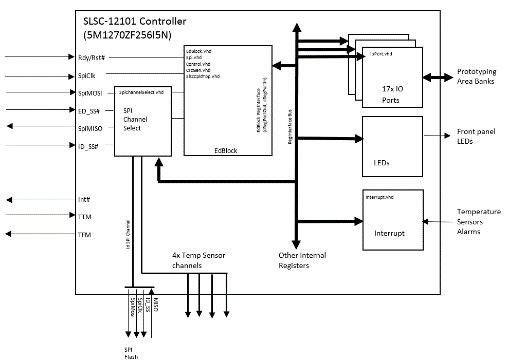

SLSC-12101 ist ein Modul zur Prototypenerstellung, das Entwicklern von SLSC-Modulen bei der schnellen Erstellung von Prototypen helfen soll. Das Modul ist in 4 Lattice-Bereiche unterteilt, in denen Benutzer Prototyp-Schaltungen erstellen können, indem sie entweder Bauteile direkt auf die Gitterstruktur löten oder eine sekundäre Schaltungskarte auf den Lattice-Bereich montieren.

Dieses Modul erfüllt alle Anforderungen zur Erfüllung der Kompatibilität von Stufe 2, wie sie in den SLSC Module Design Specifications definiert sind. Es ist so geroutet, dass es auch die Kompatibilität der Stufe 1 erreichen kann, wenn der Modulentwickler die Signalisierungsanforderungen eines vollständig kompatiblen Rear-I/O befolgt. Diese Anforderungen sind in Kapitel 11 der SLSC-Modul-Design-Dokumentation beschrieben.

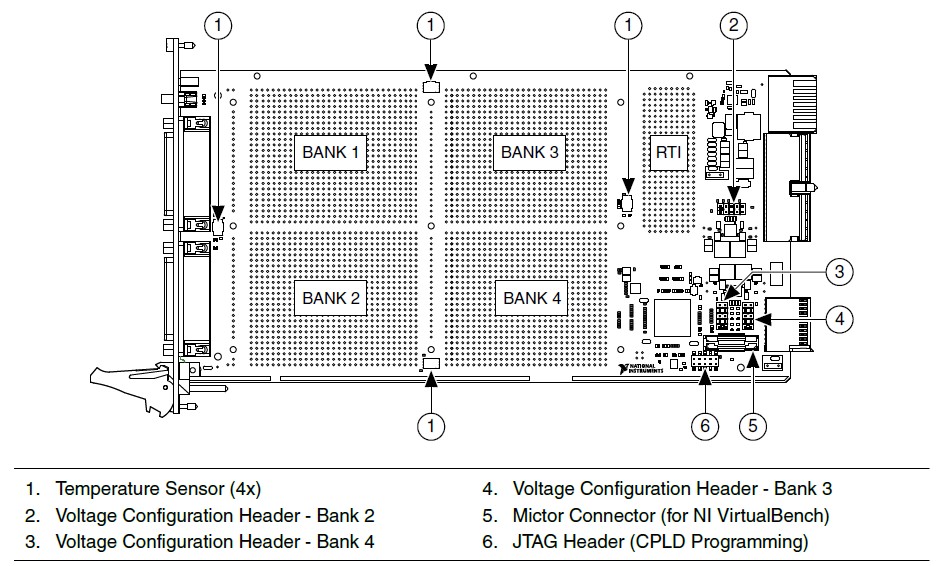

Das Prototyping-Modul verfügt über 4 Lattice-Bänke, die für die Prototypenerstellung verwendet werden können, wie in der folgenden Abbildung dargestellt:

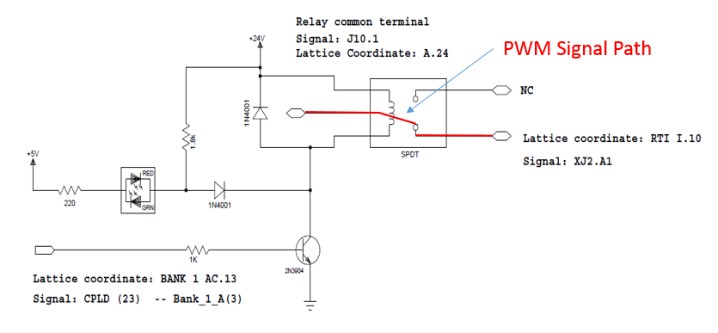

Für dieses Beispiel haben wir die unten dargestellte Schaltung auf dem Bank 1 Lattice-Bereich erstellt. Mit dieser Schaltung soll das SPDT-Relais geöffnet oder geschlossen werden, um einen offenen Stromkreis für unser PWM-Signal zu simulieren. Das Relais benötigt 24 V bei 15 mA, um das Relais mit Spannung zu versorgen, die von einem 2N3904 NPN-Transistor geliefert wird. Der Transistor wird über CPLD-Pin 23 eingeschaltet.

Folgend ist die Pinbelegung des SLSC-12101 dargestellt.

XJ2: Pin a1 = Skaliertes PWM-Ausgangssignal+ » J1 Pin1

XJ2: Pin b1 = Skaliertes PWM-Ausgangssignal+ » J1 Pin16

XJ2: Pin d1 = Skaliertes PWM-Eingangssignal+ Ausgabe » J2 Pin3

XJ2: Pin e1 = Skaliertes PWM-Eingangssignal- Zurück » J2 Pin18

RTI-12305

Das RTI 12305 wird verwendet, um die Signale von einem SLSC über einen 44-poligen Stecker vom Frontpanel des SLSC-Moduls abzubilden. Dies wird für Umgehungsverbindungen wie Fehlersimulationen oder Schaltmodule verwendet.

Externes Netzteil, HD-44-Kabel und HD-44-Anschlussblöcke

Die externe Stromversorgung erfolgt über ein 24DVC-Netzteil von NI (PSU 15). Die Signale werden mit 1 zu 1 HD-44-Kabeln zu einem Phoenix HD-44-Anschlussblock verkabelt.

Software

Die Software für dieses Projekt ist in drei Abschnitte unterteilt: Der erste Abschnitt stellt die für den SLSC-12201 erforderliche Programmierung dar. Der zweite Abschnitt zeigt den LabVIEW-Programmcode, der zur Erzeugung der PWM-Signale erforderlich ist. Im dritten Abschnitt wird beschrieben, wie der SLSC-12101 zur Fehlersimulation verwendet wird.

Programmierung des SLSC-12201

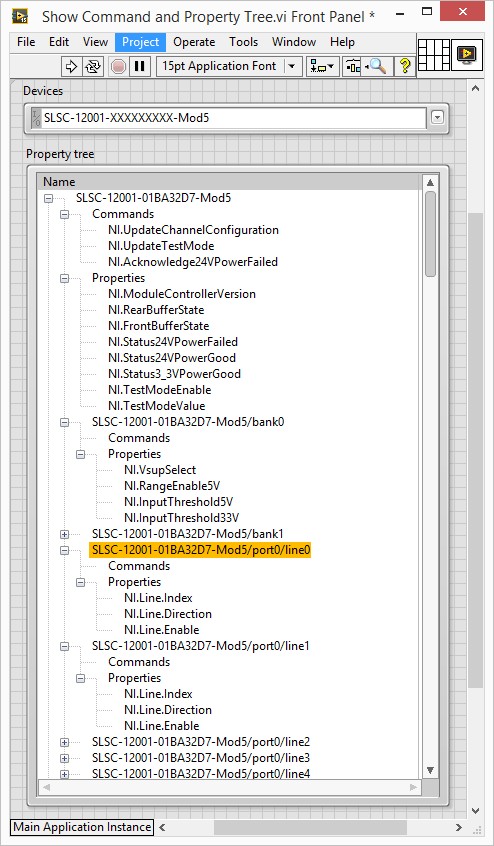

Beschreibung der Modulfunktionen

Jedes SLSC-Modul wird durch Eigenschaften und Befehle konfiguriert, die in Modulfunktionen und physikalische Kanalfunktionen unterteilt sind. Diese Funktionen werden in einem nichtflüchtiger Datenspeicher (NVRAM) auf dem Modul gespeichert und machen die Installation einer speziellen Softwareschicht zur Nutzung des Moduls überflüssig. Mit der SLSC-API können Sie die Modulfunktionen steuern.

Im mitgelieferten Beispiel „Show Command and Property Tree.vi“ kann der Benutzer alle Eigenschaften und Befehle für das Modul SLSC-12201 einsehen.

Programmierung des SLSC-12201

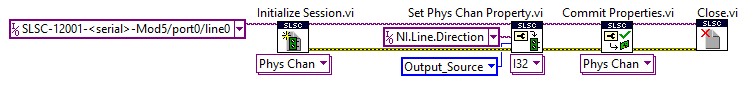

Im ersten Arbeitsschritt wird die Richtung der Leitung 0 von Port 0 als digitaler Ausgang konfiguriert. Dies ist der Pfad für die PWM-Ausgabe:

Der nächste Arbeitsschritt besteht darin, die Richtung des Ports zu einem digitalen Eingang zu konfigurieren. Dies ist der Pfad für den digitalen Eingang:

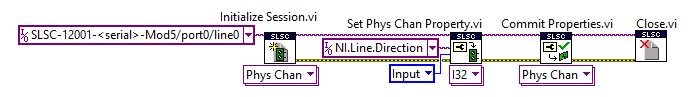

Im folgenden Programmcode wird Vsup_0 der Bank 0 zugewiesen; Vsup_0 ist mit der externen 24V-Stromversorgung verbunden. Mit diesem VI wird auch der Schwellenwert für Hoch/Tief auf 12 V gesetzt.

Wie sie sehen, wird in diesem Programmcode der Befehl NI.UpdateChannelConfiguration verwendet. Dadurch werden alle vorherigen Einstellungen übernommen und die Konfiguration der digitalen Kanäle und Bänke wird gleichzeitig aktiviert.

Programmierung des PXIe-7822R

PWM-Ausgabe

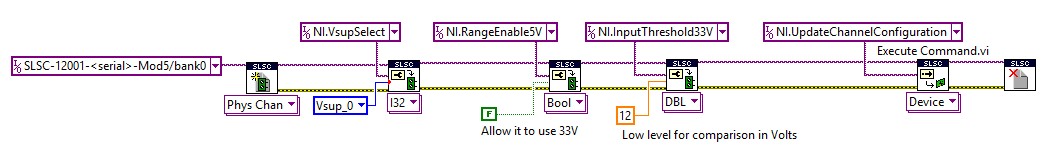

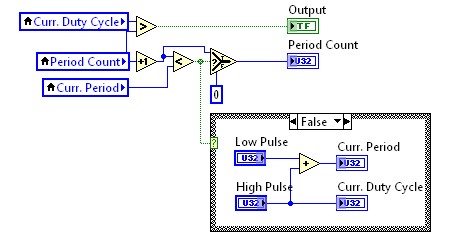

Im folgenden Programmcode für LabVIEW FPGA ist dargestellt, wie ein PWM-Ausgangssignal erzeugt wird:

Messung pulsbreitenmodulierter Signale

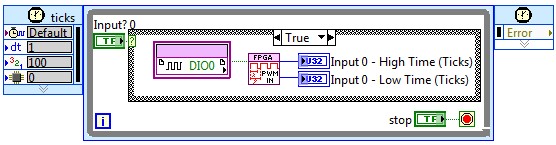

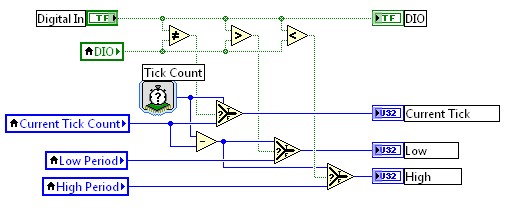

Der PWM-Eingang wird anhand des folgenden Diagramms gemessen. Einzelheiten zum Erstellen von PWM-Firmware für Geräte der R-Serie von NI finden Sie unter diesem Link: http://www.ni.com/example/5963/en/

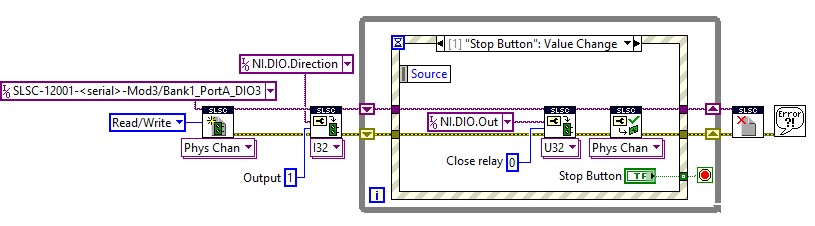

Programmierung des SLSC-12101 und der Host-Anwendung

Trennmodul

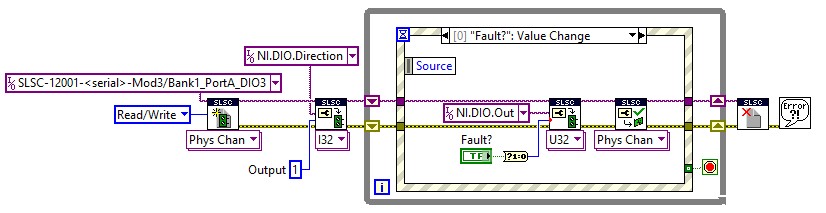

Dieser Programmcode steuert das Relais und kann Fehler im offenen Stromkreis einfügen, wann immer der Benutzer es wünscht oder wenn dieser die Testsuite programmiert. In diesem Programmcode wird eine Ereignisstruktur verwendet (um unnötigen Datenverkehr mit dem SLSC-Chassis zu vermeiden):

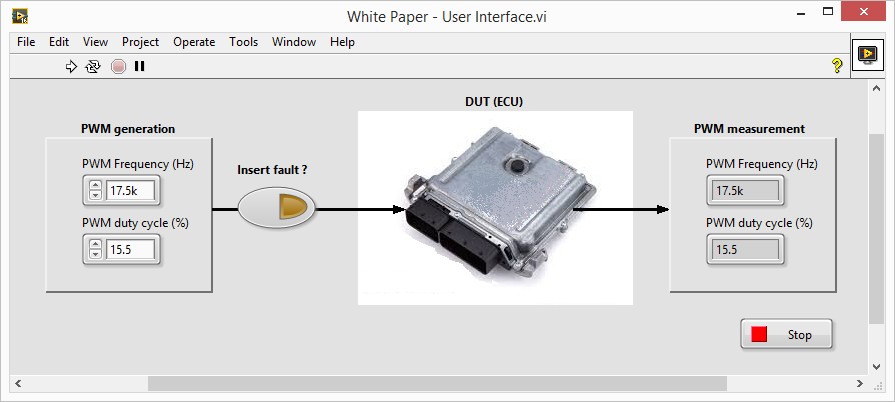

Host-Anwendung

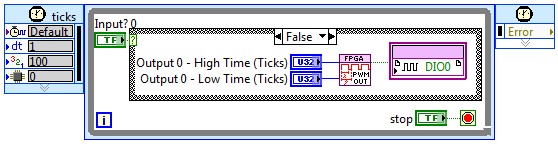

Das endgültige System für diese einfache Anwendung ist nachfolgend abgebildet. Darin wird das Frontpanel von LabVIEW dargestellt.

Fazit

In diesem Dokument wird demonstriert, wie mithilfe der SLSC-Architektur von NI zusätzliche Komponenten in den Signalpfad eines Prüfsystems eingefügt werden können.

Anhang 1: Hardwaresystemkomponenten

Im Folgenden sind die verwendeten Hardware- und Softwarekomponenten aufgelistet:

|

Artikel |

PN |

Name |

Beschreibung |

Hersteller |

Anz. |

|

1 |

781622-01 |

PXIe-1078 |

PXI-Chassis mit 9 Steckplätzen |

NI |

1 |

|

2 |

783003-04 |

PXIe-8840 |

PXIe-Controller mit Windows (64 Bit) |

NI |

1 |

|

3 |

783486-01 |

PXIe-7822R |

FPGA-Modul der PXIe R-Serie |

NI |

1 |

|

4 |

156166-01 |

SHC68-C68-RDIO2 |

Geschirmtes High-Speed-Digitalkabel der R-Serie, 1 m |

NI |

1 |

|

5 |

784532-01 |

SLSC-12001 |

SLSC-Chassis mit 12 Steckplätzen |

NI |

1 |

|

6 |

785369-01 |

RTI 12301 |

RTI DIO 32 für SHC68-C68-RDIO2 |

NI |

1 |

|

7 |

785356-01 |

SLSC-12201 |

DIO-Modul SLSC-12201 (33 V) mit Schwellenwertbildung | ||

|

8 |

CS-DSDHD44MF0-005 |

HD44-Kabel |

44-poliges (HD44) „Deluxe HD D-Sub“-Kabel – kupfergeschirmt – Stecker/Buchse |

Amphenol |

2 |

|

9 |

SET-Artikelnummer: |

RTI-12305 |

RTI-12305 für HD44-Anschluss |

FESTLEGEN |

1 |

|

10 |

785204-01 |

SLSC-12101 |

Prototyping-Modul |

NI |

1 |

|

11 |

781093-01 |

NI PS15 |

Externes Netzteil mit 24 V |

NI |

1 |

|

12 |

Artikelnummer: 2322427 |

HD44-Anschlussblock |

HD44-Anschlussblock MFG von Phoenix Contact |

Phoenix Contact |

1 |

Anhang 2: Quellen

- SLSC-Modul-Design-Dokumentation (erhältlich von NI beim Kauf von PN 785205-01)

- SLSC-12001: Erste-Schritte-Leitfaden und Spezifikationen

- SLSC-12201: Erste-Schritte-Leitfaden

- SLSC-12101: Benutzerhandbuch

- Beispiel Pulsbreitenmodulation DAQ Personality