# Digital Avionics Interface Selection: Simplifying a Not So Simple Choice

### Wednesday, May 25<sup>th</sup> – 9:00am

Brandon Treece, NI

Nathan Johnson-Williams, New Wave DV

Digital Avionics Interface Selection: Simplifying a Not So Simple Choice

Brandon Treece Chief Solutions Marketing Manager Electronics Test, Defense Aircraft Aerospace, Defense, and Government NI

# Digital Avionics Interfaces Span Platform Assets

### Generic Interfaces

### High-Speed/ Backbone Interfaces

Application-Specific Interfaces

MIL-STD-1553 Serial Rapid

ARINC 818 COCKPIT VIDEO DISPLAY

MIL-STD-1553 F-35 ON-BOARD DATA HANDLING Serial RapidIO®

ni.com

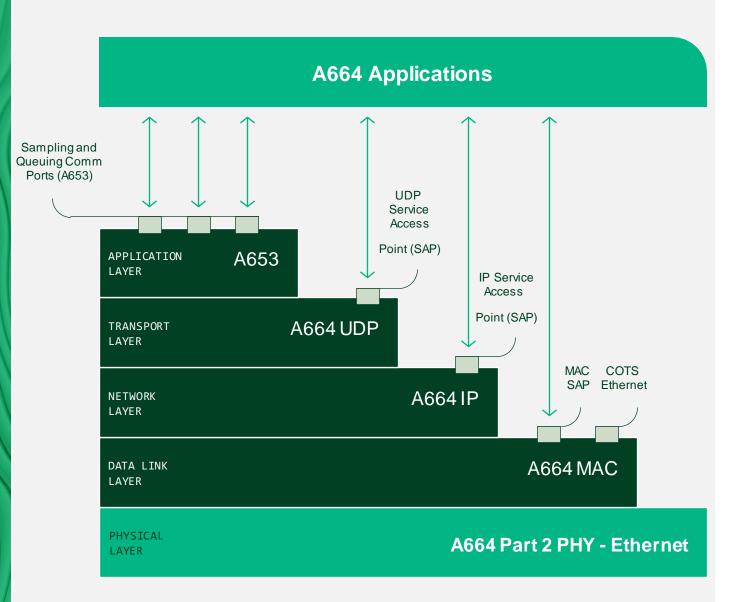

OSI LAYERS OF ARINC-664P7/AFDX

Generic Digital Avionics Bus Interfaces

Commoditization has led to little differentiation in vendor hardware offerings

Test equipment vendors differentiate at the higher layers of the OSI stack

Manufacturing and Depot test requirements typically don't require advanced software features

NI offers interfaces for MIL-STD-1553, ARINC 429, RS232/422/485, and CANbus

### Generic Interfaces

### High-Speed/ Backbone Interfaces

Application-Specific Interfaces

MIL-STD-1553 Serial Rapid

ARINC 818 COCKPIT VIDEO DISPLAY

MIL-STD-1553 F-35 ON-BOARD DATA HANDLING Serial RapidIO®

ni.com

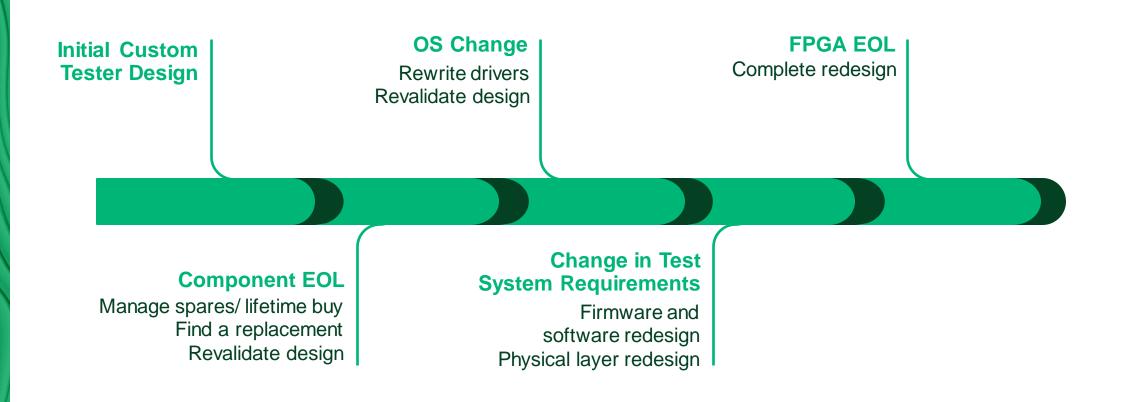

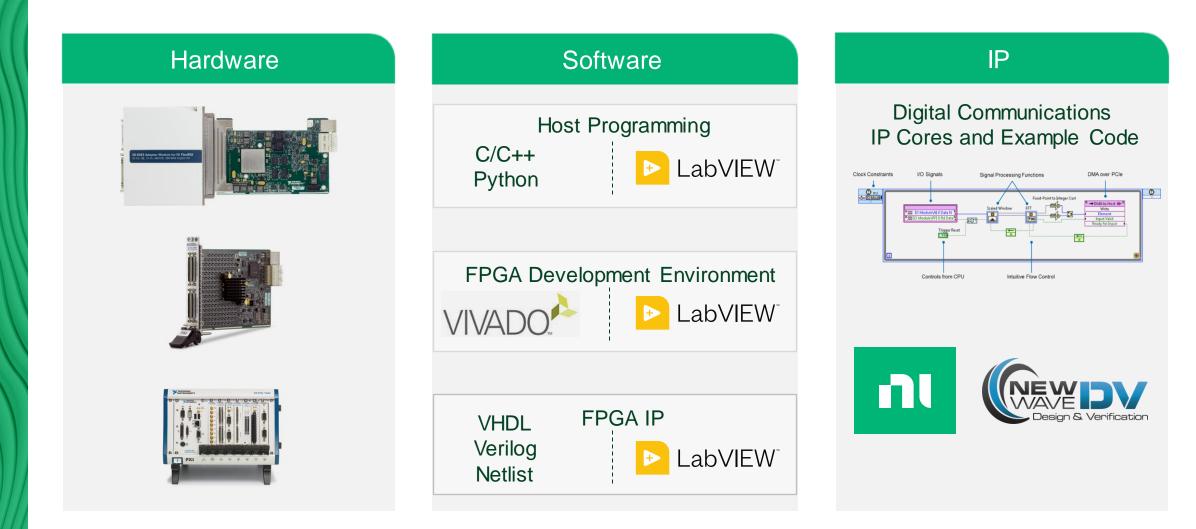

## Numerous Approaches to Incorporating FPGAs

The wrong approach leads to risk of increases support burden over time

Develop your own hardware and IP from scratch

Use a COTS FPGA development board, and write your own IP

Use a COTS FPGA development board, and off-the-shelf IP core

Use a COTS FPGAenabled PXI module, and write your own IP

Use a COTS FPGAenabled PXI module, and off-the-shelf IP core

### Life-Cycle Management of a "Homegrown" Test System

## Numerous Approaches to Incorporating FPGAs

The wrong approach leads to risk of increases support burden over time

Develop your own hardware and IP from scratch

Use a COTS FPGA development board, and write your own IP

Use a COTS FPGA development board, and off-the-shelf IP core

Use a COTS FPGAenabled PXI module, and write your own IP

Use a COTS FPGAenabled PXI module, and off-the-shelf IP core

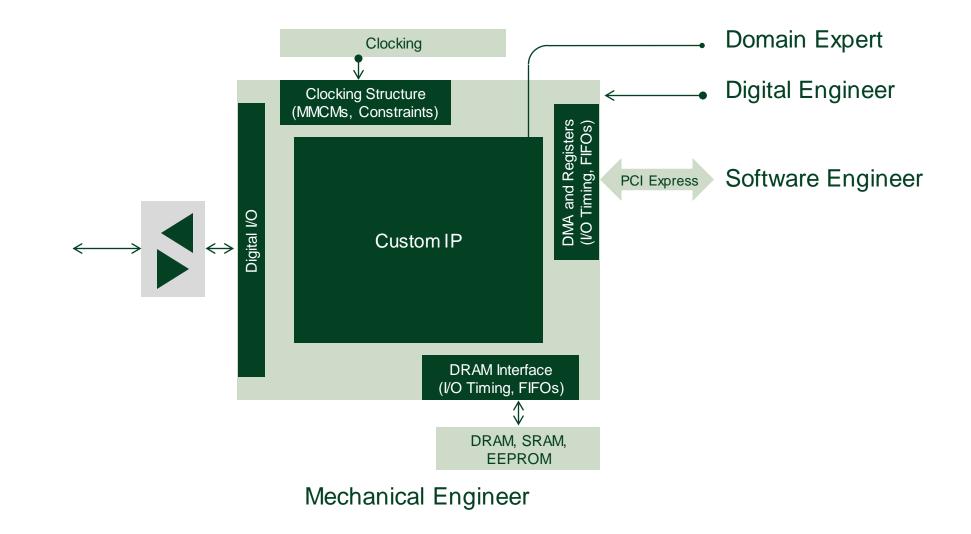

### Typical Custom Design With I/O

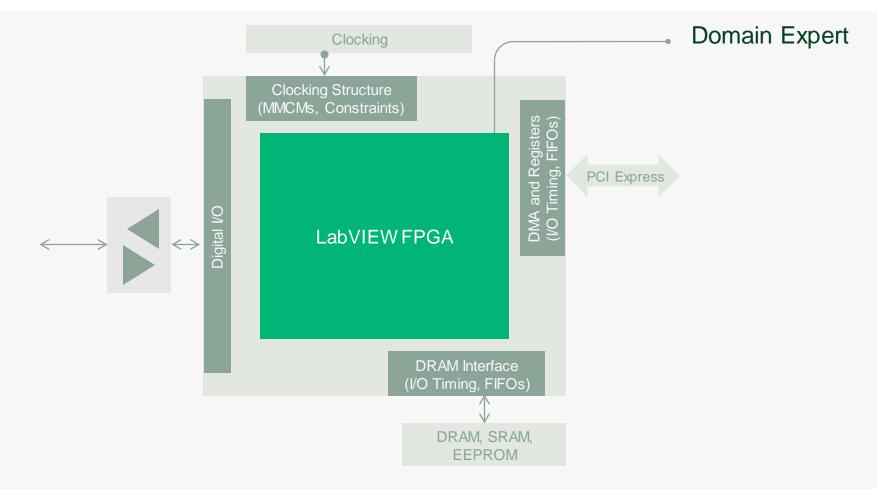

## NI's Approach to FPGA Design

### Focus on your IP with LabVIEW FPGA

### NI Tools for FPGA-Based Digital Avionics Interfacing

### FPGA-Based Digital Interfacing in PXI

Reconfigurable I/O High-Density SE Digital

High-Speed Serial High-Speed Serial (MGT interface)

FlexRIO Custom Instruments High-Performance SE, Differential Digital, and Custom I/O

### NI Tools for FPGA-Based Digital Avionics Interfacing

ni.com

## Company Overview

New Wave DV is the leading expert in high-speed serial interfaces. Our expertise allows us to move data effectively and efficiently from data producer to consumer. With a focus on industry leading performance and environmental durability, our products are the perfect fit for defense and aerospace applications.

#### **Our Mission**

Enable our Partners to Change the World

#### **About New Wave DV**

Privately held, +60 employees Headquartered in Minneapolis, Minnesota. Second Office in Colorado Springs, Colorado Core competency is FPGA network engineering Local outsourced manufacturing ITAR certification Strong commitment to customer's support and responsiveness Long product life cycle

### New Wave DV Products

| IP Cores                    |

|-----------------------------|

| Ethernet                    |

| Fibre Channel               |

| ARINC 818                   |

| Mil1394 (1394b AS5643)      |

| SerialFPDP                  |

| HOTLink II                  |

| High Speed Data Bus (HSDB)  |

| Serial RapidIO <sup>®</sup> |

#### **High-Speed Serial Interface Boards**

High Speed Serial Cores on NI PXIe cards

Windows & Linux OS software support

Custom variants welcomed

NI PXIe cards pre-loaded with New Wave DV's IP

#### **Platforms & Appliances**

Interface Analysis, Test, Record, Playback

Configurable/Selectable port counts, speed, storage space, environmentals

Full IP Core Suite support

Precision-built for maintenance, sustainment, and test applications

#### **Engineering Services**

Solutions can be based on existing NWDV products or all-new. We will analyze your requirements, leverage existing hardware and IP cores where possible, create new where required, and ultimately deliver <u>your</u> solution.

#### Ethernet ExpressXG

#### Mil1394

PHY

OHCI Link Layer Controller GP2Lynx Link Layer 1394b AS5643 Link Layer Controller

### **Fibre Channel**

Link Layer Anonymous Subscriber Messaging FC Upper Layer Protocol

#### Serial Front Panel Data Port

sFPDP Link Layer sFPDP Express NEW WAVE DESIGN & VERIFICATION

## New Wave DV IP Cores

New Wave's FPGA/Interface Cores can be provided pre-loaded on NI Serial Instruments to provide a turn-key solution. They are also available stand-alone for your custom development.

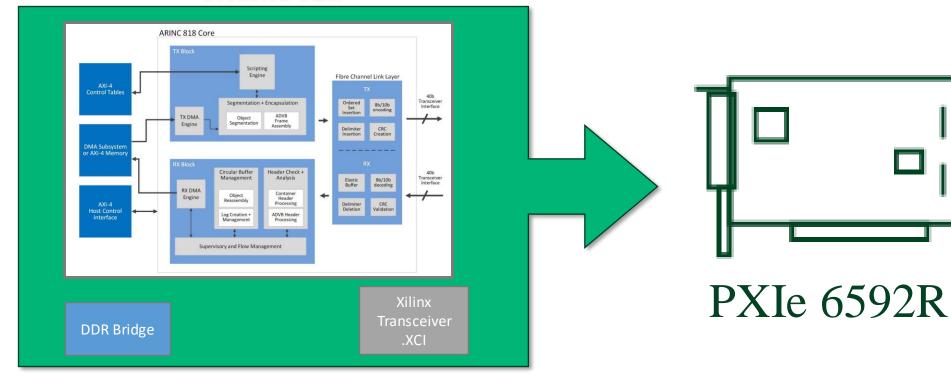

### ARINC 818

ARINC 818 DMA ARINC 818 Stream

#### **Additional Protocols**

Serial RapidIO<sup>®</sup> HOTLink II High Speed Data Bus

## Advantages of Applications on NI FPGA

- Quickest path to HDL on Hardware

- NI FPGA provides accessory IP

- Directly interface with HDL IO

- No Driver Development

- Application Natively in LabVIEW

- No C/C++ Require

| ₩ tx_clk0                     | 1                |                            |  |  |

|-------------------------------|------------------|----------------------------|--|--|

| <pre> # tx_dcm_locked </pre>  | 1                |                            |  |  |

| > 👹 tx_ifg_delay[7:0]         | 00               | 00                         |  |  |

| tx_statistics_valid           | 0                |                            |  |  |

| > Wtx_statistics_vector[25:0] | 0000000          | 0000000                    |  |  |

| H xgmacint                    | 0                |                            |  |  |

| > 👹 xgmii_rxc[7:0]            | 11               | 11                         |  |  |

| > 💆 xgmii_rxd[63:0]           | 0100009c0100009c | 0100009c0100009c           |  |  |

| > 🖬 xgmii_txc[7:0]            | 11               | ff / 11                    |  |  |

| > 🖬 xgmii_txd[63:0]           | 0200009c0200009c | 070707070 0200009c0200009c |  |  |

HDL Code or IP

#### NI FPGA Hardware

LabVIEW Application

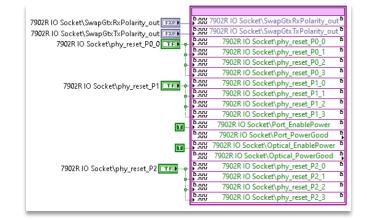

## Directly Control Top-Level IO

| phy_reset_P0_0 | : | in | <pre>std_logic;</pre> |

|----------------|---|----|-----------------------|

| phy_reset_P0_1 | : | in | <pre>std_logic;</pre> |

| phy_reset_P0_2 | : | in | <pre>std_logic;</pre> |

| phy_reset_P0_3 | : | in | <pre>std_logic;</pre> |

| phy_reset_P1_0 | : | in | <pre>std_logic;</pre> |

| phy_reset_P1_1 | : | in | <pre>std_logic;</pre> |

| phy_reset_P1_2 | : | in | <pre>std_logic;</pre> |

| phy_reset_P1_3 | : | in | <pre>std_logic;</pre> |

| phy_reset_P2_0 | : | in | <pre>std_logic;</pre> |

| phy_reset_P2_1 | : | in | <pre>std logic;</pre> |

| phy reset P2 2 | : | in | <pre>std logic;</pre> |

| phy_reset_P2_3 | : | in | <pre>std_logic;</pre> |

|                |   |    |                       |

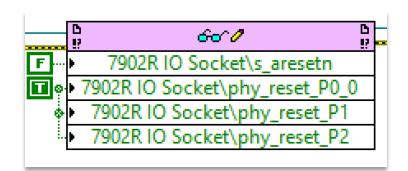

Route the signals to the top level of the Socketed CLIP

Within a single cycle loop connect controls/indicators to your top level signals Directly read/write the signals in LabVIEW

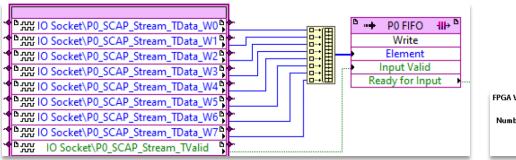

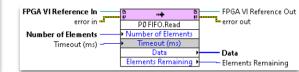

### DMA to Host

| P0_SCAP_Stream_TValid: out s | td_logic;                      |        |                   |

|------------------------------|--------------------------------|--------|-------------------|

| P0_SCAP_Stream_TReady: in st | d_logic;                       |        |                   |

| P0_SCAP_Stream_TData_W0: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W1: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W2: out | std_logic_vector(63            | downto | 0);               |

| P0_SCAP_Stream_TData_W3: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W4: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W5: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W6: out | <pre>std_logic_vector(63</pre> | downto | 0);               |

| P0_SCAP_Stream_TData_W7: out | <pre>std_logic_vector(63</pre> | downto | <mark>0)</mark> ; |

|                              |                                |        |                   |

Route the signals to the top level of the Socketed CLIP

Within a single cycle loop connect controls/indicators to your top level signals Directly read/write the signals in LabVIEW

## AXI-LITE Read/Write

| s_axi_awaddr             | : in std_logic_vector(31 downto 0);   |

|--------------------------|---------------------------------------|

| s axi awvalid            | : in std logic;                       |

| s_axi_awready            | : out std_logic;                      |

| s axi wdata              | : in std logic vector (31 downto 0);  |

| s axi wvalid             | : in std logic;                       |

| s_axi_wready             | : out std logic;                      |

| s axi wstrb              | : in std logic vector (3 downto 0);   |

| axi bvalid               | : out std logic;                      |

| s_axi_bready             | : in std logic;                       |

| s axi bresp              | : out std logic vector(1 downto 0);   |

| s_axi_araddr             | : in std logic vector (31 downto 0);  |

| axi arvalid              | : in std logic;                       |

| axi arready              | : out std logic;                      |

| s axi rdata              | : out std logic vector (31 downto 0); |

| s <sup>a</sup> xi rvalid | : out std logic;                      |

| s_axi_rready             | : in std logic;                       |

| s axi rresp              | : out std logic vector (1 downto 0);  |

Route the AXI signals to the top level of the Socketed CLIP

Follow the example designs to connect the AXI signals

⅓ reg.host instruction fifo 0 💌

÷,

4000000

FXP < +,32,32 >

\* **G**

t-œ

tE

1/2 60MHz

400000

7902R IO Socket\s\_axi\_araddr 7902R IO Socket\s\_axi\_arvalid 7902R IO Socket\s\_axi\_arready

7902R IO Socket\s\_axi\_rdata

7902R IO Socket\s\_axi\_rvalid

7902R IO Socket\s axi rready

7902R IO Socket\s axi awadd

7902B IO Socket\s axi avavali

7902R IO Socket\s axi awrea

7902B-IO Socket\s axi wdata

7902R IO Socket\s axi bre

7902R IO Socket\s axi rres

LabVIEW provides VIs to read and write registers on the AXI Bus. **N**

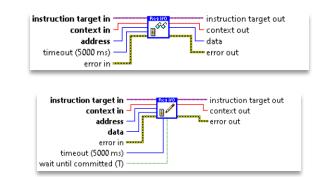

## Example ARINC-818

Socketed CLIP

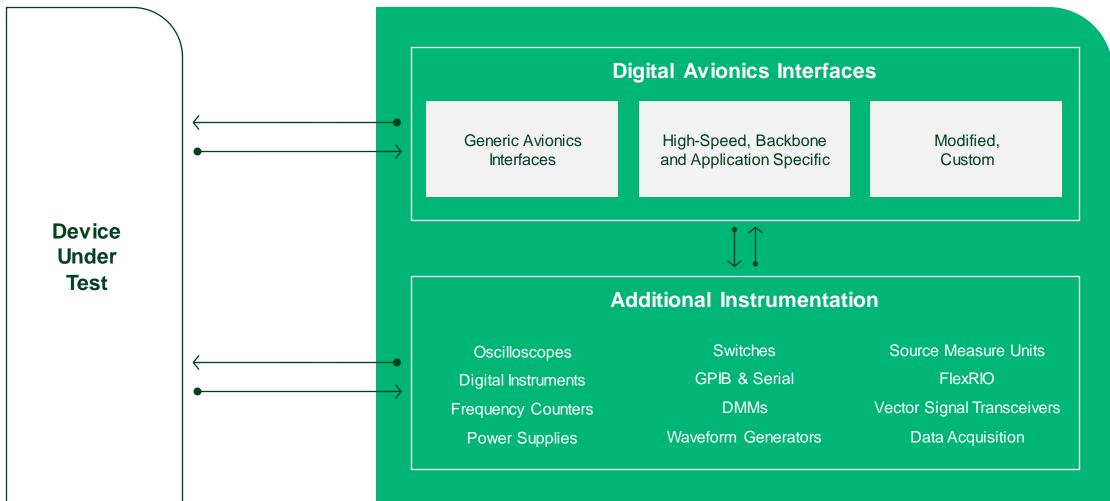

#### **NI PXI-BASED ATS**

## Summary

Digital avionics interfaces are routinely not considered with the same level of rigor as other instrumentation

While generic interfaces have become commoditized, high-speed and application specific protocols can introduce significant technical challenges

Whenever possible, test engineers should avoid custom solutions for manufacturing & depot test by leveraging COTS hardware, software, and IP

NI's customizable COTS hardware and software platform, along with key industry partnerships gives you customizability without additional design and maintenance cost, along with the system integration benefits of PXI