Using Wideband IF Digitizers to Solve Challenges in Streaming and Recording RF Signals

Überblick

Contents

- The Challenge

- Wideband Streaming

- Narrowband Streaming

- Phase Noise Considerations and Improvements

- Conclusion

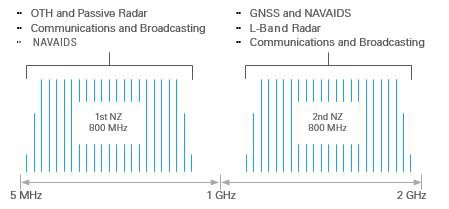

Figure 1. Example Signals in 5 MHz–2 GHz Band

The Challenge

Many applications in verification and validation tests, spectrum surveillance, multiconstellation GNSS, and software-defined receivers require acquisition, real-time processing, and recording of RF signals. Modern analog-to-digital converter (ADC) technology enables direct sampling receivers operating at or above 2 GHz. This simplifies the architecture of the receivers, mainly in the case of multichannel systems, which require tight synchronization between channels. That is the case in direction finding systems for spectrum surveillance, over-the-horizon and passive radar, and antenna measurements.

Furthermore, the increasing demand for faster spectrum scanning and new types of radar requires receivers with wide instantaneous bandwidth and real-time signal processing.

Normally, current RF streaming systems take two forms: high-bandwidth, lossless streaming and narrowband streaming. The first type records all available bandwidth, which in modern applications implies gigabytes per second of data for systems sampling at 2 GS/s or higher. Active radar systems typically take advantage of wideband streaming.

Often, however, most of the useful information concentrates around a particular narrower band. This is where the second type of streaming comes in. Narrowband streaming enables data reduction and inline signal processing. Such systems require streaming to HDD signals that occupy relatively narrow bands with several central frequencies.

Example narrowband signals acquired, streamed, and analyzed (or recorded) by passive radar applications can originate from Digital Video Broadcasting—Terrestrial (DVB-T) or Advanced Television Systems Committee (ATSC) transmitters that are characterized by bandwidths of 6 MHz to 8 MHz, depending on the country, and are in VHF/UHF frequency ranges.

GNSS multiconstellation receiver tests are other examples for narrowband streaming, where the requirement is to use both GPS L5/L2 and GLONASS G1 and G2 signals. Users might focus their interest in signals that are only a few megahertz wide but that can be spaced even hundreds of megahertz apart.

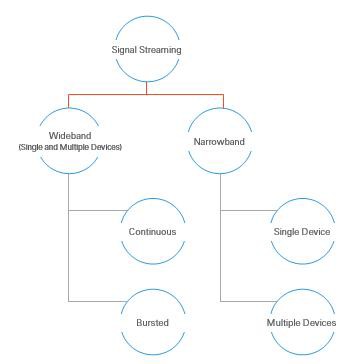

Figure 2. Classification of Streaming Applications Covered in This Document

After acquiring these wideband signals, these streaming systems require subsequent downconversion (shift in frequency), decimation, equalization, and calibration. The resulting narrowband signal then gets demodulated and decoded, further filtered, amplified, and stored to HDD or any combination of these functions.

At a high level, typical streaming and channelizing applications can be divided as figure 2 shows.

Wideband Streaming

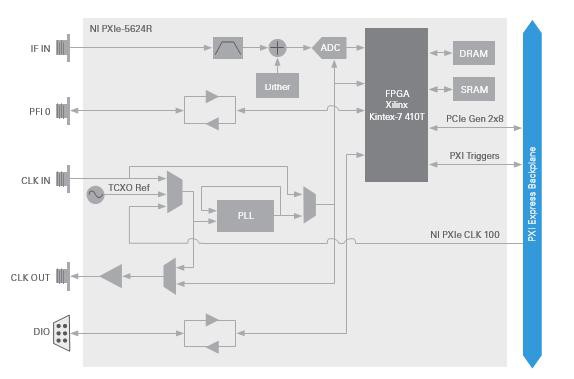

Um die Herausforderungen bei der Breitbandübertragung besser zu verstehen, müssen zunächst die technischen Spezifikationen des ZF-Empfängers klar sein. In diesem Whitepaper geht es um das Modul PXIe-5624R. In der Regel sind ZF-Empfänger Bestandteil des Vektorsignalanalysators, der den Mischer, den ZF-Empfänger und die Signalquellen für den Lokaloszillator umfasst. Die Architektur des als Beispiel verwendeten Vektorsignalanalysators wird im Whitepaper Einführung zum leistungsstarken Breitband-Signalanalysator PXIe-5668R bis 26,5 GHz vorgestellt.

Die Zwischenfrequenz (ZF) liegt im Frequenzbereich von 5 MHz bis 2 GHz und hat eine typische Bandbreite von 800 MHz (s. technische Spezifikationen). Nachdem ein bandbegrenztes Rauschsignal hinzugefügt wurde, mit dem die Auswirkung der Quantisierung des A/D-Wandlers reduziert und die spektrale Leistung verbessert wird, tastet der A/D-Wandler das Signal bei bis zu 2 GS/s mit einer Auflösung von 12 bit ab. Der integrierte FPGA verarbeitet diese Samples und überträgt die Daten über eine PCI-Express-Schnittstelle der 2. Generation an andere Geräte (PXI-Express-Controller, RAID). Dadurch ist ein Daten-Streaming mit theoretischen Raten von bis zu 4 GB/s möglich. Im Falle der Breitbandübertragung führt der FPGA nur eine digitale Abwärtswandlung für alle eingehenden Daten aus. Beim Schmalband erfolgen mehrere unabhängige Abwärtswandlungen, worauf im Verlauf dieses Dokuments noch eingegangen wird.

Abb. 3: Blockdiagramm des ZF-Digitizers PXIe-5624R

Das Packen von Bits

Beim Thema Breitbandübertragung muss nicht nur die theoretisch verfügbare Bandbreite der PCI-Express-Schnittstelle betrachtet werden, auch die praktischen Einschränkungen (durch die Steuerbefehle, die über denselben Bus verschickt werden) spielen eine Rolle. Die erste und einfachere Implementierung für das Versenden von Daten über die PCI-Express-Schnittstelle besteht darin, 16-bit-Samples zu verschicken, und zwar eines nach dem anderen, auch wenn die Daten vom A/D-Wandler nur 12 bit groß sind. Diese Herangehensweise führt jedoch zu einer theoretischen Begrenzung von 4 GB/s pro verfügbarer PCI-Express-Verbindung des PXIe-5624R-Moduls (2 Byte/Samples bei 2 GS/s entsprechen 4 GB/s), sodass in der Praxis kein kontinuierliches Streaming möglich wäre. Dafür gibt es jedoch eine clevere Lösung: das Packen von Bits. Damit können vier 12-bit-Samples in drei 16 bit lange Wörter gepackt werden. Durch diese Methode wird die Datenrate von 4 GB/s auf 3 GB/s reduziert, wodurch ein kontinuierliches Daten-Streaming möglich ist.

Synchronisierung zwischen Modulen

Häufig müssen Daten von mehreren Modulen desselben Typs kontinuierlich übertragen werden. Diese synchronisierten RF-Systeme mit mehreren Kanälen ermöglichen bestimmte Anwendungen, wie z. B. die Richtungsbestimmung. Mithilfe einer Analyse der Phasendifferenz des eingehenden Signals zwischen unterschiedlichen Kanälen kann das System die Richtung der Signalquelle bestimmen.

In einem solchen Fall werden die Digitizer mit demselben Referenztakt gekoppelt. Das ist standardmäßig der 100-MHz-Takt der PXI-Express-Backplane. So ist es dank Synchronisierung möglich, die Erfassung auf mehreren Geräten zur selben Zeit zu starten oder genauer gesagt mit einer relativen Verschiebung von wenigen 10 ps. Wichtig dabei ist, dass der Versatz zwischen den Digitizern bei jeder Ausführung derselbe ist, solange die Temperatur dieselbe ist, damit der Versatz mittels Kalibrierung korrigiert werden kann. Die Synchronisierung ist ohne Timing-Modul oder externe Verkabelung möglich. Sie nutzt zwei Trigger-Leitungen der PXI-Express-Backplane.

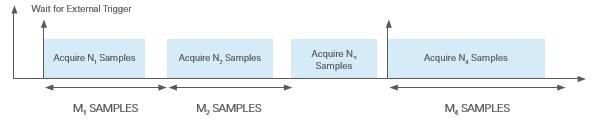

Burst-Modus

Im Burst-Modus werden Daten erst nach Auftreten des Triggersignals an den Host übertragen. Das Triggersignal kann über den PFI0-Anschluss direkt mit dem ZF-Digitizer verbunden oder über einen Software-Trigger ausgelöst werden. Im Burst-Modus kann der Anwender die Logik des FPGAs so festlegen, dass einige Parameter konfigurierbar sind:

- Datensatzlänge (Nx)

- Datensatzdauer (Mx)

- Anzahl der Aufzeichnungen pro Trigger

- Anzahl der Samples vor dem Trigger

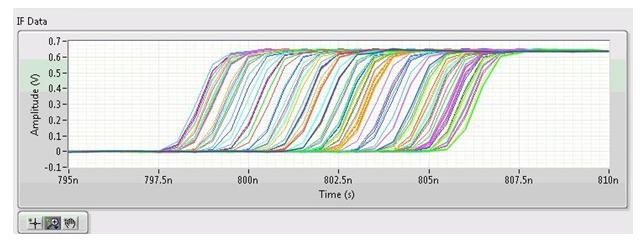

Abb. 4: Beispiel einer Burst-Erfassung

Ein Burst-Szenario lässt sich so implementieren, dass verschiedene Datensatzlängen und Verzögerungen möglich sind. Beschreibungen der Szenarien können auf dem Host-Gerät definiert und später an den FPGA übertragen werden. Das Triggersignal kann allerdings Samples mit einer Abweichung von etwa 8 ns erzeugen, da das PFI0-Signal selbst mit 125 MHz abgetastet wird.

Abb. 5: Triggerabweichung aufgrund der Abtastung von PFI0 bei 125 MHz

Narrowband Streaming

Narrowband streaming is often needed in GNSS validation, spectrum monitoring, passive radar, and direction finding applications. In such cases, users often are interested in multiple relatively narrowband signals that are within a defined, larger spectrum component and often coming from multiple spatially distributed antennas.

The strong requirement is that the signals are acquired simultaneously, which makes it impossible to use traditional, swept vector signal analyzers. The solution for such a challenge is called a channelizer—the application that acquires a wideband signal containing all narrowband signals of interest and then separates them using DDC on an FPGA, thereby significantly reducing data rates.

Digital Downconversion

Because of its parallel structure, it is possible to implement numerous DDC logic blocks on an FPGA, allowing for the simultaneous analysis of multiple narrowband signals. The first stage of DDC uses a digital quadrature mixer that shifts a signal to baseband from any frequency within the range of the digitizer. The next stage decimates (reduces the sample rate). Programmable digital FIR lowpass filters prior to each stage of decimation prevent aliasing when the sample rate is reduced. Users can retrieve the decimated data as in-phase and quadrature.

Additionally, users can perform digital signal processing for the digital correction of analog imperfections in the system such as:

- Digital Gain—Digitally controls the I and Q signal amplitudes

- Digital Offset—Digitally controls the I and Q signal offsets

- Equalization—Filters the I/Q data to equalize the analog response of a device

- I/Q Impairments—Modifies the I/Q data to correct or apply I/Q impairments such as gain imbalance, quadrature skew, or DC offset

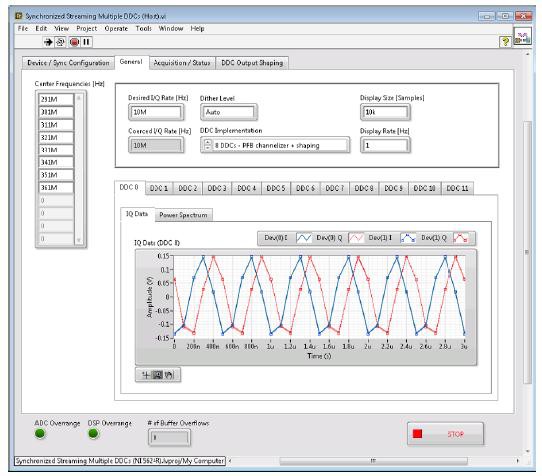

One PXIe-5624R device with its Xilinx Kintex-7 XC7K410T can fit up to 12 DDCs with 37.5 MHz I/Q rates or 8 DDCs with 93.75 MHz I/Q rate (contact NI for details). Subbands can be streamed to RAID and/or analyzed online on the host machine.

Multiantenna DDC Using IF Receivers

As mentioned above, multiple PXIe-5624R devices can be synchronized for acquisition from multiple antennas, for example, for direction finding applications. In such cases, users can define up to 12 center frequencies with selected I/Q rates and multiple IF modules will downconvert signals from multiple antennas. The PXI Express solution simplifies the synchronization of the multiple PXIe-5624R ADCs.

- The following parameters can be set in such case:

- Channels’ center frequencies

- Channels’ I/Q rate

- ADC clock source

- Clock out

- Burst size (for burst acquisition)

- Burst wait period in samples

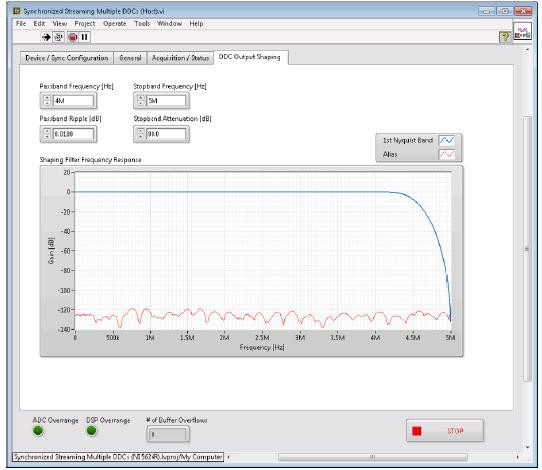

- Shaping filter’s parameter

Figure 6. Example Configuration Window for a Multimodule, Multichannel Channelizer Application

Figure 7. Shaping Filter’s Parameters

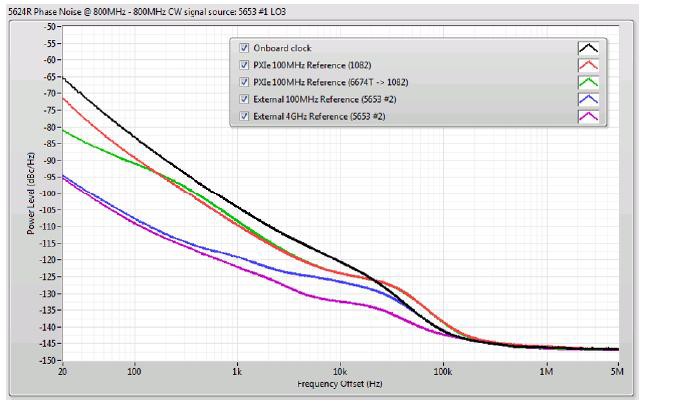

Figure 8. Various Options for Phase Noise Reduction

Phase Noise Considerations and Improvements

The open architecture of the PXIe-5624R IF receivers allows for using external clock signals in applications where keeping the phase noise to a minimum plays a critical role. Users can choose the best way of providing clocking signals to ADC, depending on the requirement of the system and available budget. Figure 8 shows various possible configurations of clock sourcing. The PXIe-6674T module is a timing and synchronization module developed for multimodule, multichassis systems (phase noise marked with green on Figure 8), whereas PXIe-5653 is a low-phase noise LOs generator (marked with blue and purple on Figure 8). Lowest phase noise is achieved with the PXIe-5653 module, whereas PXIe-6674T is a compromise between cost and performance.

Conclusion

NI’s PXI-based IF receivers (PXIe-5624R) with built-in FPGAs are powerful devices that empower some of the most demanding streaming applications such as radar test, GNSS validation, agile spectrum monitoring, and direction finding. Their open architecture in combination with the power of the PXI platform allow for easy expansion into multiple channels with guaranteed phase synchronization and coherence.

Furthermore, the NI modular approach allows users to add components such as mixers (with central frequencies up to 26.5 GHz in PXI Express form factor or 72 GHz to 76 GHz radio head), switches, power amplifiers/attenuators, and preselector modules.